## Chapter 3: Sequential Devices

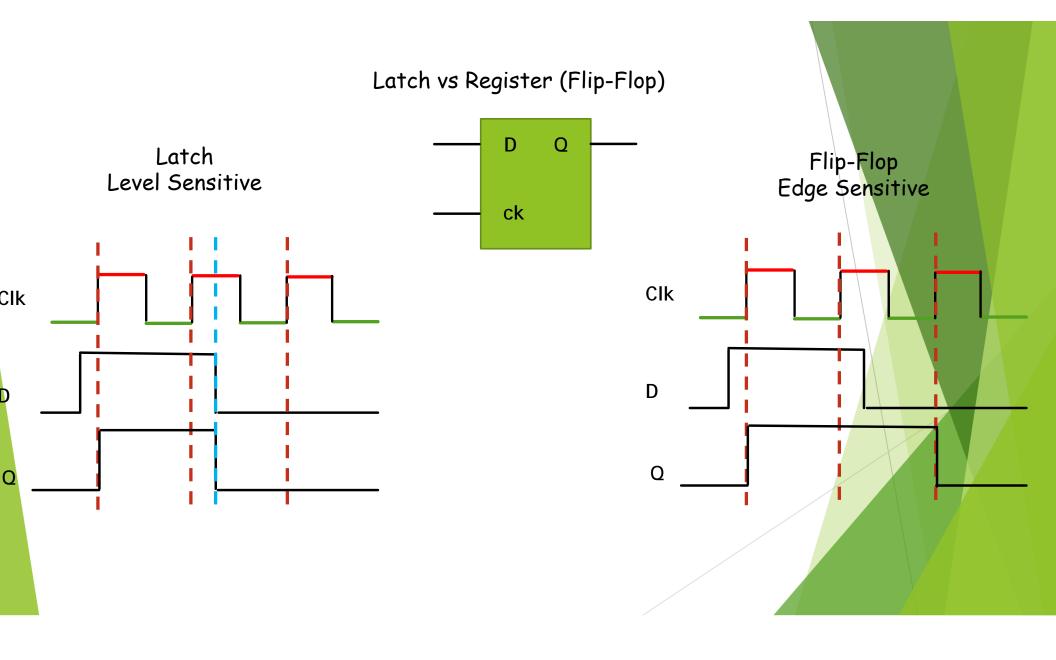

- Sequential circuits, unlike combinational ones whose outputs depend only on the present inputs, the outputs depend on present as well as past inputs. Sequential circuits would require memory while combinational circuits which are memoryless.

- The building blocks , main devices, used in designing and implementing sequential circuits are Flop-Flops.

• In this chapter we will:

- Understand the design and working principles of Latches and Flip-Flops.

- Understand the importance and significance of sequential circuits in general.

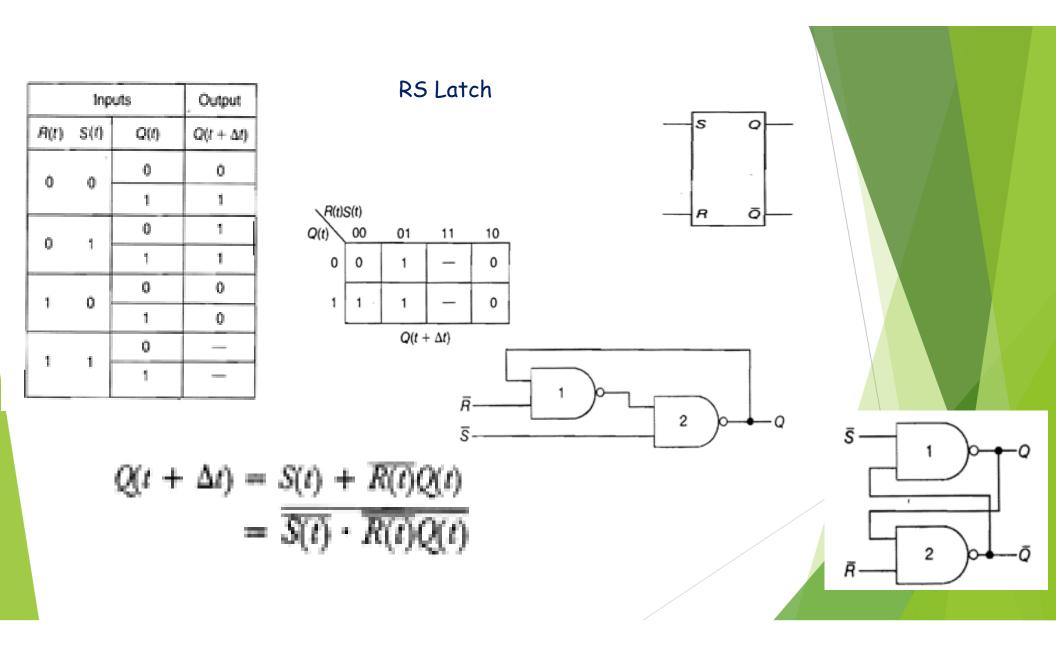

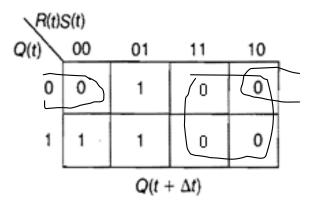

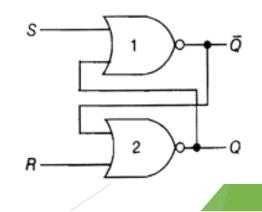

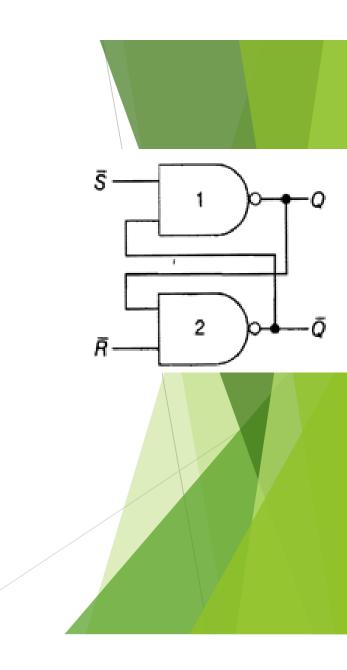

## Let us assume the outputs of the forbidden state to be zeros

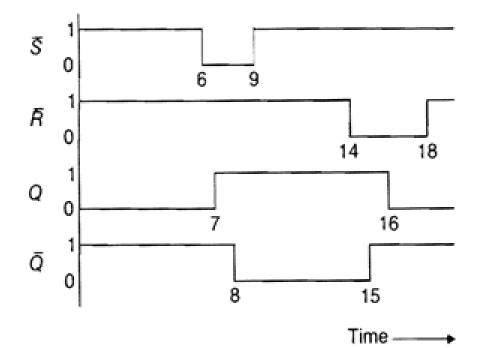

$$Q(t + \Delta t) = \overline{R(t)} [Q(t) + s(t)]$$

$$= \overline{R(t)} + \overline{[Q(t) + S(t)]}$$

### Distributed delay

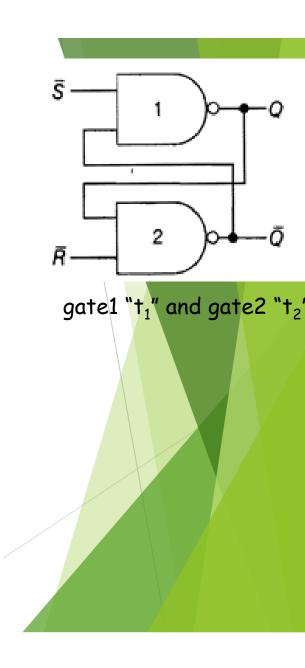

$$Q(t + t_1) = \overline{S(t) \cdot Q(t)} = S(t) + Q(t)$$

$$\overline{Q}(t + t_2) = \overline{R(t) \cdot Q(t)} = R(t) + \overline{Q}(t)$$

$$\overline{Q}(t + t_1 + t_2) = \overline{R(t + t_1) \cdot Q(t + t_1)}$$

$$= \overline{R(t + t_1) [S(t) + Q(t)]}$$

$$Q(t + t_1 + t_2) = \overline{R}(t + t_1)[S(t) + Q(t)]$$

$$t_1 = t_2 = \Delta t$$

$$Q(t + \Delta t) = \overline{R} \left( t + \frac{\Delta t}{2} \right) [S(t) + Q(t)]$$

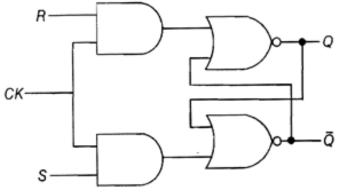

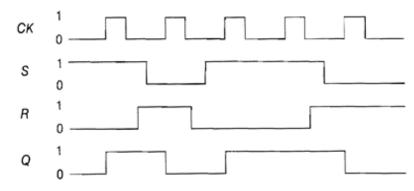

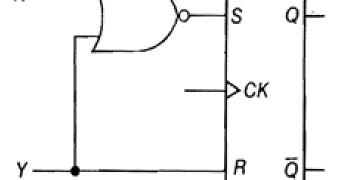

#### Clocked SR flip-flop

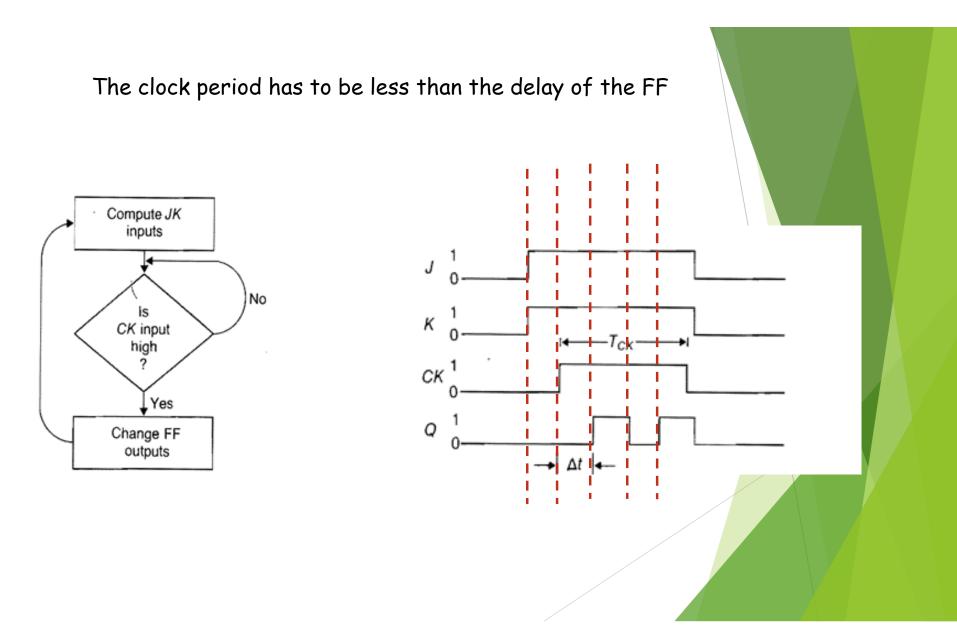

- Dependable operation of FFs must include clocks

- The Clock input forces an action to take place only when the clock is present, otherwise outputs are forced to remain unchanaed

|       | Inputs |      |           | Out               | Outputs                      |  |  |  |

|-------|--------|------|-----------|-------------------|------------------------------|--|--|--|

| CK(t) | S(t)   | R(t) | Mode      | $Q(t + \Delta t)$ | $\overline{Q}(t + \Delta t)$ |  |  |  |

| 0     |        | -    | No action | Q(t)              | $\overline{Q}(t)$            |  |  |  |

| л     | 0      | 0    | Hold      | Q(t)              | $\overline{Q}(t)$            |  |  |  |

| л     | 0      | 1    | Reset     | 0                 | 1                            |  |  |  |

| л     | 1      | 0    | Set       | 1                 | 0                            |  |  |  |

| л     | 1      | 1    | Invalid   | -                 | -                            |  |  |  |

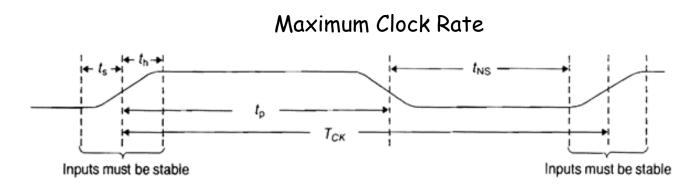

$$T_{ck} \geq t_s + t_p + t_{NS}$$

t<sub>s</sub> : setup time, inputs have be there for some time before triggering

- t<sub>p</sub>: propagation delay

- t<sub>NS</sub> : Delay of Next-State Decoder

$$f_{CK} = \frac{1}{T_{CK}} \le \frac{1}{t_{\rm s} + t_{\rm p} + t_{\rm NS}}$$

Example: Modify the SR flip-flop to accept "11" as a RESET state.

| X(t) | Y(t) | Q(t) | $Q(t + \Delta t)$ |

|------|------|------|-------------------|

| 0    | 0    | 0    | 1                 |

| 0    | 0    | 1    | 1                 |

| 0    | 1    | 0    | 0                 |

| 0    | 1    | 1    | 0                 |

| 1    | 0    | 0    | 0                 |

| 1    | 0    | 1    | 1                 |

| 1    | 1    | 0    | 0                 |

| 1    | 1    | 1    | 0                 |

|      |      |      |                   |

KM:  $Q(t + \Delta t) = \overline{X}(t)\overline{Y}(t) + \overline{Y}(t)Q(t)$

Х

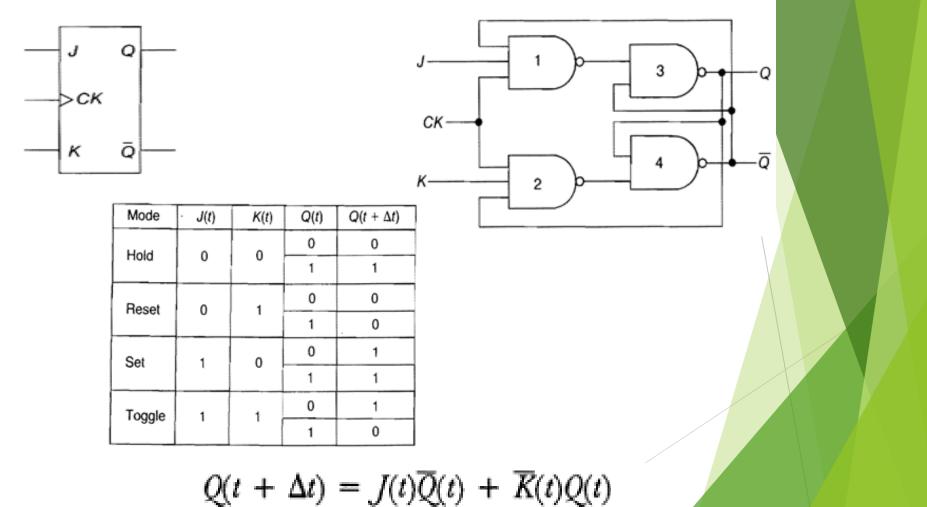

An alternative good way is to let the "11" state to make the FF toggle, JK flip-flop

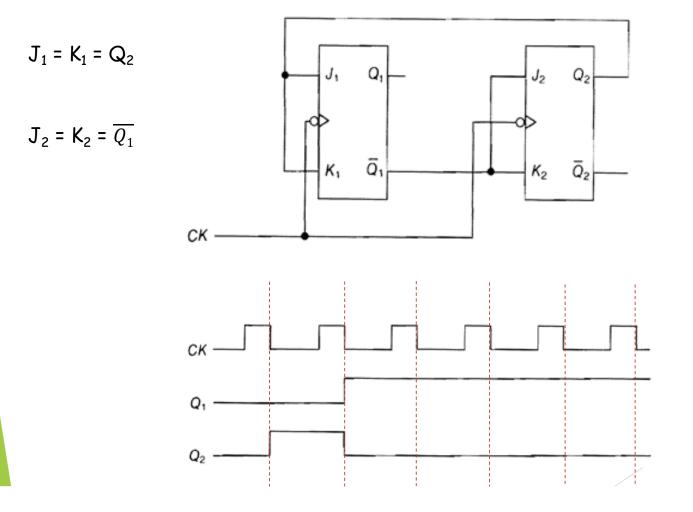

Example:Obtain the timing diagram for the sequential circuit shown for at least six clock cycles. Assume that  $Q_1(0) Q_2(0) = 00$

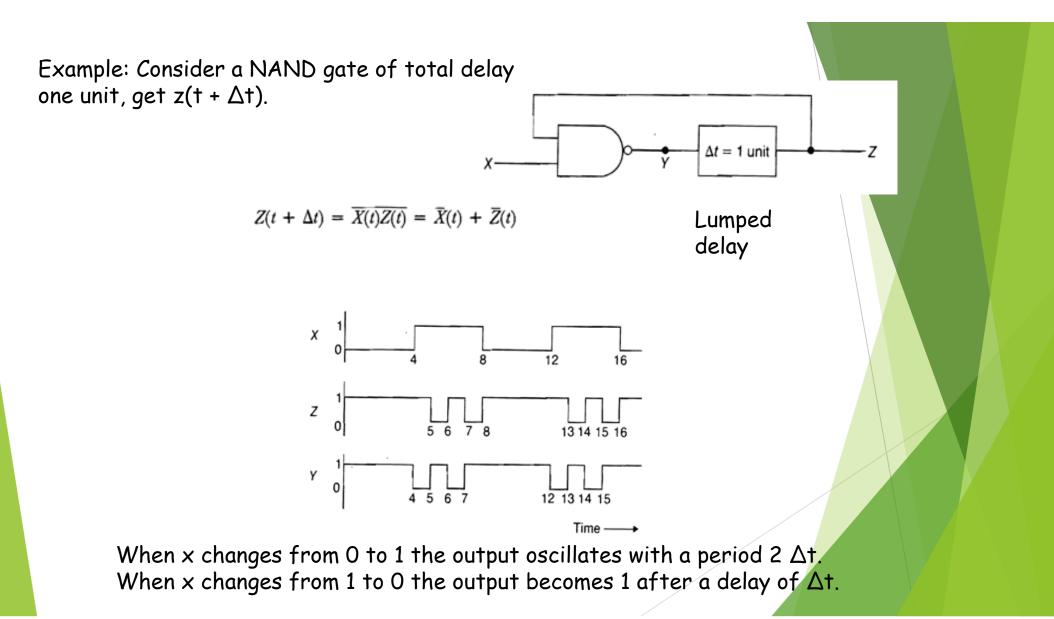

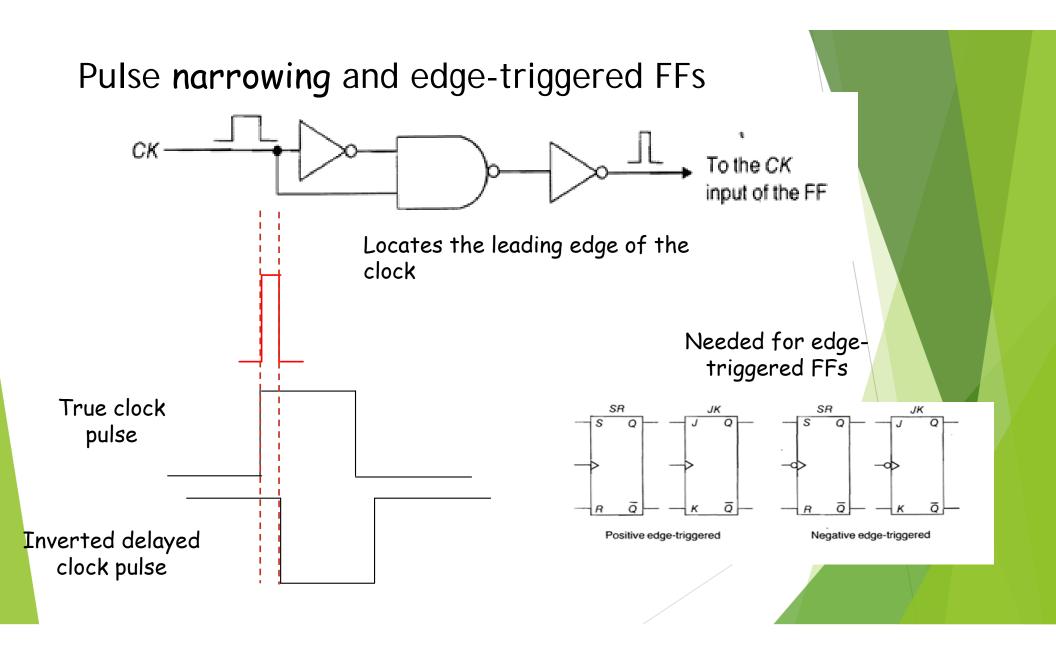

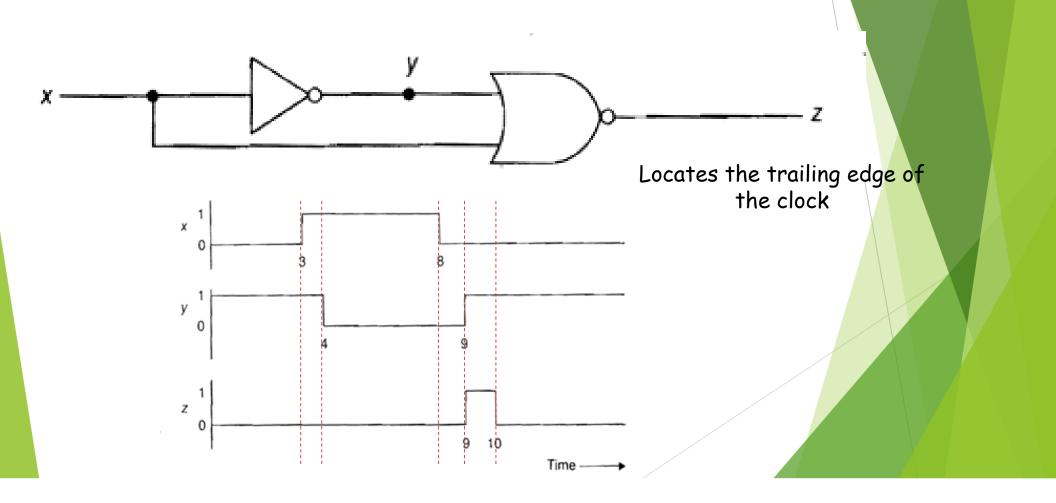

Obtain the response of the shown circuit, where each of the gates is assumed to have 1 unit of gate delay. The input x remains high for a duration longer than 5 units.

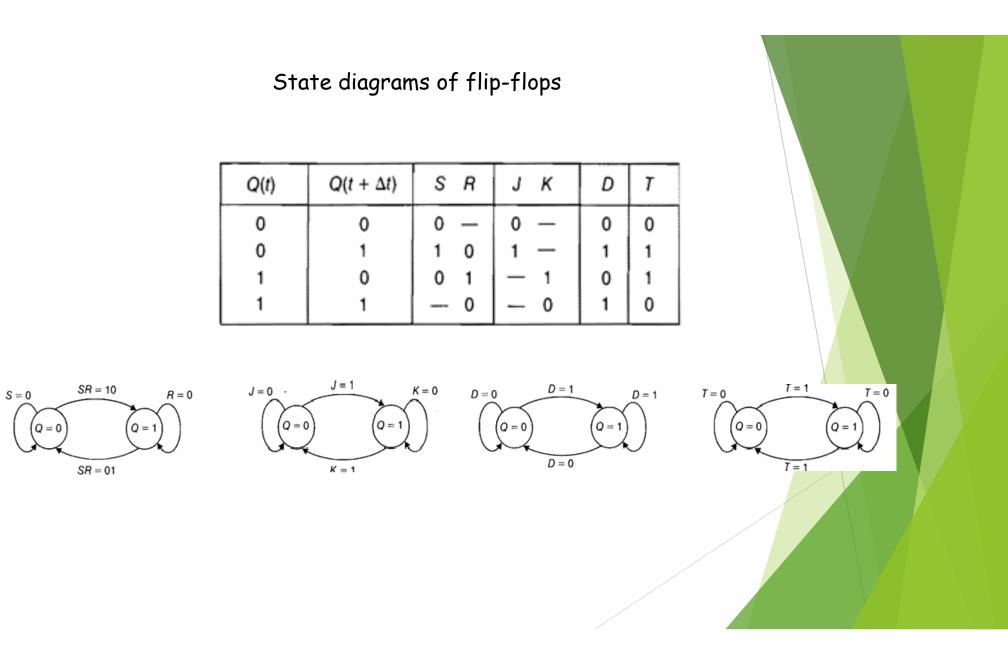

The memory circuit of sequential circuits is composed mainly of flip-flops.

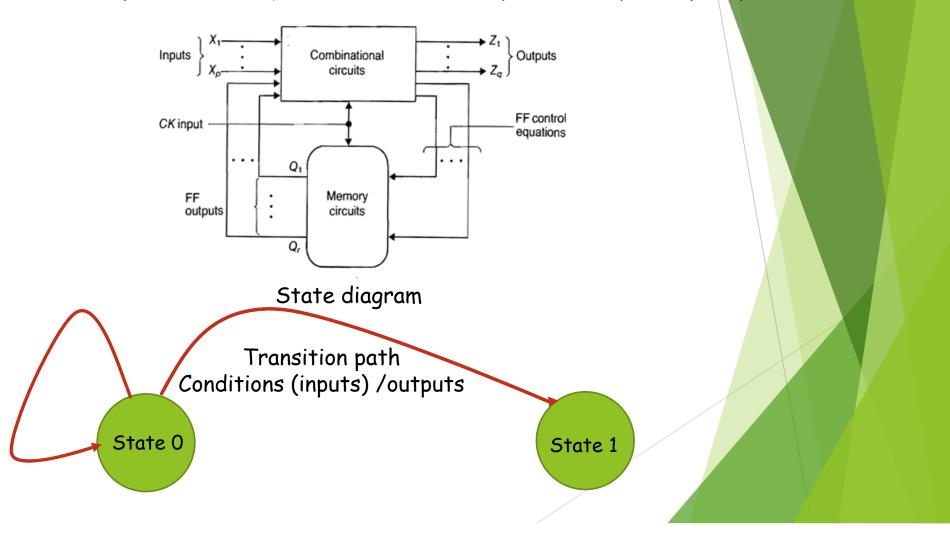

# Chapter 4: Design of Synchronous Sequential Circuits

By the end of this chapter we should be able to

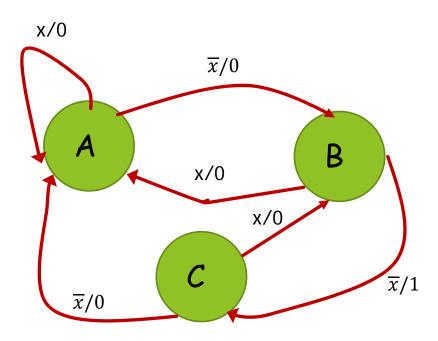

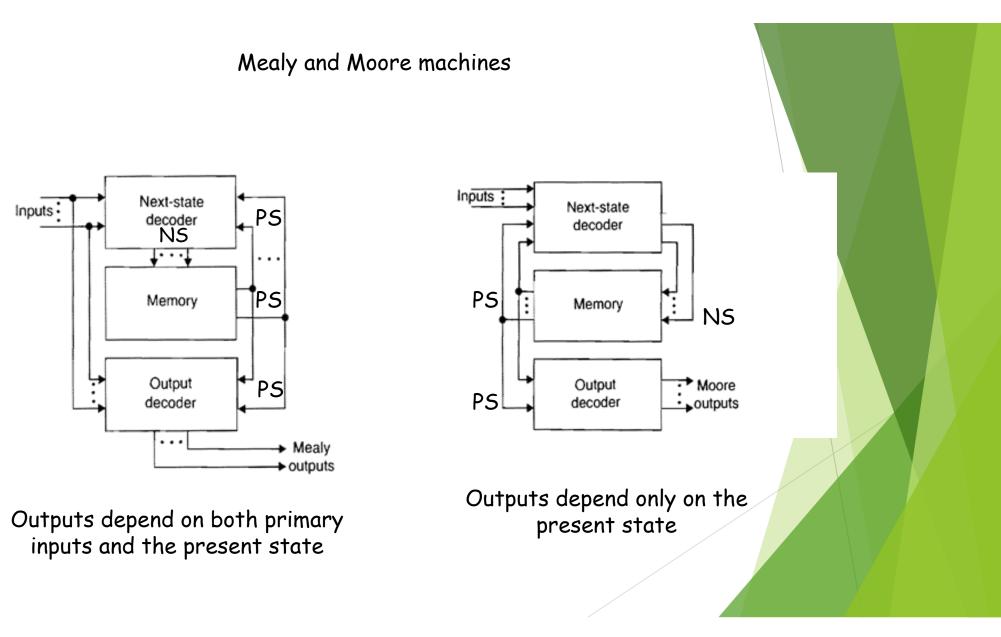

- Differentiate between Mealy and Moore finite-state machines

- >Obtain a state diagram for a sequential circuit design

- Follow the different design steps to realize the synchronous sequential machine

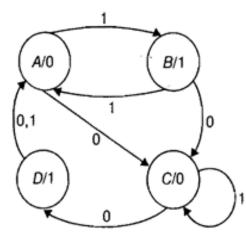

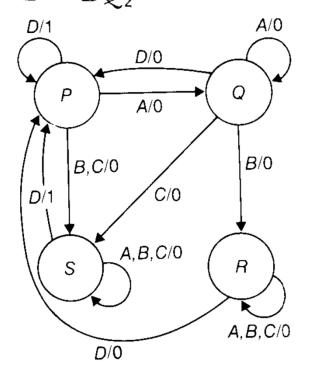

#### State Diagram and State Table

| Present<br>state | Next state NS, outputs |       |  |  |  |

|------------------|------------------------|-------|--|--|--|

| PS               | X = 0                  | X = 1 |  |  |  |

| A                | Β, Ο                   | A, 0  |  |  |  |

| В                | C,1                    | A,0   |  |  |  |

| С                | A, 0                   | В,О   |  |  |  |

|                  |                        |       |  |  |  |

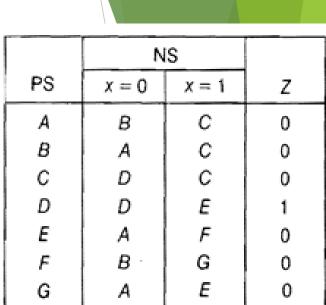

State Diagram and State Table

|             | N            | IS           |   |

|-------------|--------------|--------------|---|

| PS          | <i>x</i> = 0 | <i>x</i> = 1 | Z |

| Α           | С            | В            | 0 |

| B<br>C<br>D | С            | A<br>C       | 1 |

| С           | D            |              | 0 |

| D           | А            | А            | 1 |

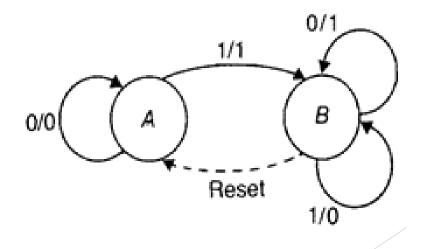

Example: Obtain the state diagram of a controller for a serial machine that performs the 2's complement operation .

### 1100110101010000

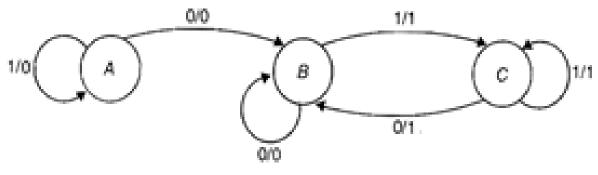

Example: Obtain the state table for synchronous sequential machine that detects a 01 sequence. The detection of sequence sets the output, Z=1, which is reset only by a 00 input sequence.

|    | NS           | NS, Z        |  |  |  |  |

|----|--------------|--------------|--|--|--|--|

| PS | <i>x</i> = 0 | <i>x</i> = 1 |  |  |  |  |

| A  | B.0          | A,0          |  |  |  |  |

| В  | <i>B</i> ,0  | C,1          |  |  |  |  |

| C  | <i>B</i> ,1  | C,1          |  |  |  |  |

Example: Obtain the Moore equivalent state table for the Mealy machine

|    | NS           | 6, Z         |

|----|--------------|--------------|

| PS | <i>x</i> = 0 | <i>x</i> = 1 |

| A  | C,0          | A,0          |

| В  | B,0          | A,0          |

| c  | D,1          | C,1          |

| D  | D,0          | <i>B</i> ,0  |

| E  | C,1          | A,0          |

|    |              |              |

|    | N            | S, Z         |

|----|--------------|--------------|

| PS | <i>x</i> = 0 | <i>x</i> = 1 |

| A  | C',0         | A,0          |

| В  | <i>B</i> ,0  | A,0          |

| C' | D",1         | C",1         |

| C" | D",1         | C",1         |

| D' | D',0         | B,0          |

| D" | D',0         | B,0          |

| Ε  | C",1         | A,0          |

|          | N            |                           |   |

|----------|--------------|---------------------------|---|

| PS       | <i>x</i> = 0 | <i>x</i> = 0 <i>x</i> = 1 |   |

| А        | C'           | A                         | 0 |

| В        | В            | A                         | 0 |

| C'       | D"           | А<br>С"<br>С              | 0 |

| C"<br>D' | D"           | C"                        | 1 |

| D'       | D'           | В                         | 0 |

| D"       | D'           | В                         | 1 |

| Е        | D'<br>C"     | A                         | — |

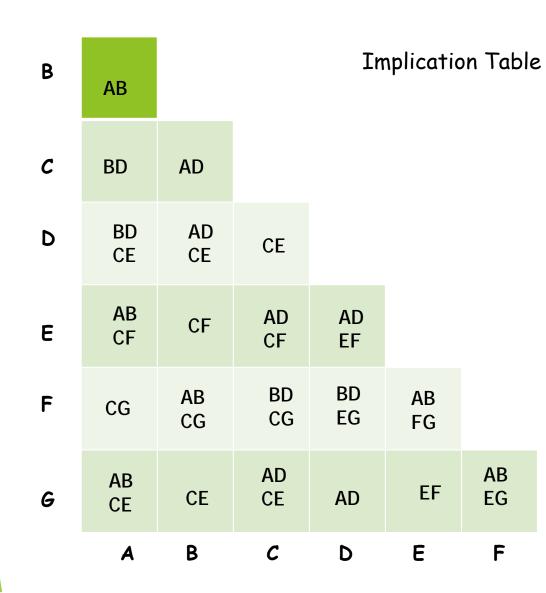

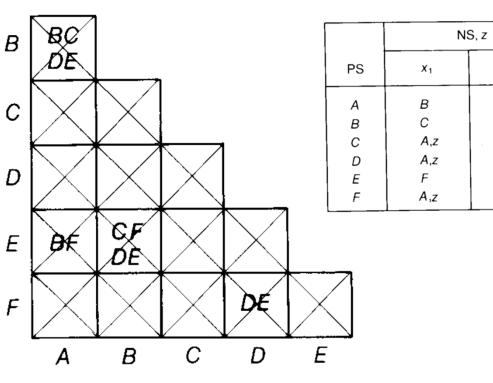

### Eliminating Redundant States

|    | N     |        |   |  |

|----|-------|--------|---|--|

| PS | x = 0 | x = 1  | Z |  |

| А  | В     | С      | 0 |  |

| В  | A     | С      | 0 |  |

| С  | D     | с<br>с | 0 |  |

| D  | D     | Е      | 1 |  |

| Ε  | А     | F      | 0 |  |

| F  | B     | G      | 0 |  |

| G  | A     | Ε      | 0 |  |

|    |       |        |   |  |

Are any two states equivalent? So, do we have any redundant state?

Equivalent States:

>Have the same output

>Make the same transition

|    | N     | S     |   |

|----|-------|-------|---|

| PS | x = 0 | x = 1 | Z |

| А  | В     | С     | 0 |

| В  | А     | С     | 0 |

| С  | D     | С     | 0 |

| D  | D     | Е     | 1 |

| Ε  | А     | F     | 0 |

| F  | B     | G     | 0 |

| G  | А     | E     | 0 |

|    | N     | IS     |   |

|----|-------|--------|---|

| PS | x = 0 | x = 1  | Z |

| A  | В     | С      | 0 |

| В  | А     | с<br>с | 0 |

| C  | D     |        | 0 |

| D  | D     | E      | 1 |

| E  | А     | F      | 0 |

| F  | B     | G      | 0 |

| G  | А     | Ε      | 0 |

|    |       |        |   |

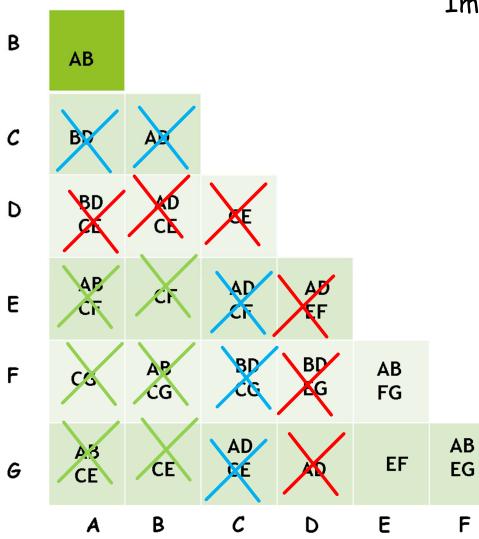

### Implication Table

|   | Partitio        | on Tab | le        |          |           |            |          |          |  |  |

|---|-----------------|--------|-----------|----------|-----------|------------|----------|----------|--|--|

|   |                 | В      | АВ        |          |           |            |          |          |  |  |

| F | (F <i>G</i> )   | с      | Br        | AI       |           |            |          |          |  |  |

| Е | (EFG)           | D      | BD        |          | X         |            |          |          |  |  |

| D | (EF <i>G</i> )  |        | AP        |          |           |            |          |          |  |  |

| С | (EF <i>G</i> )  | E      | CT        | Cr       | CT.       | <b>F</b> F |          |          |  |  |

| В | (EF <i>G</i> )  | F      | C/S       | A₽<br>CG | BD<br>CC  | BD         | AB<br>FG |          |  |  |

| A | (AB)(EFG)       | G      | A.3<br>CE | CE       | AD<br>ITE | X          | EF       | AB<br>EG |  |  |

|   | (AB)(C)(D)(EFG) |        | A         | В        | с         | D          | E        | F        |  |  |

|   |                 |        |           |          |           |            |          |          |  |  |

|        | N     |        |   |  |

|--------|-------|--------|---|--|

| PS     | x = 0 | x = 1  | Z |  |

| А      | А     | с<br>с | 0 |  |

| A<br>C | D     |        | 0 |  |

| D      | D     | Е      | 1 |  |

| Ε      | А     | Ε      | 0 |  |

Reduced State Diagram and State Table

(AB)(C)(D)(EFG)

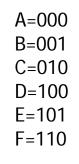

n: FFs m: States  $m \le 2^n$

| PS       | N            |              |   |

|----------|--------------|--------------|---|

| $Q_1Q_2$ | <i>x</i> = 0 | <i>x</i> = 1 | Ζ |

| 00       | 00           | 01           | 0 |

| 01       | 11           | 01           | 0 |

| 11       | 11           | 10           | 1 |

| 10       | 00           | 10           | 0 |

|          |              |              |   |

State Transition Table

A = 00, C = 01, D = 11, and E = 10

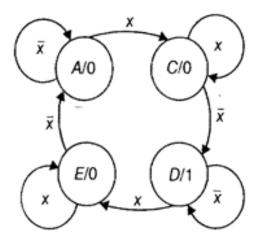

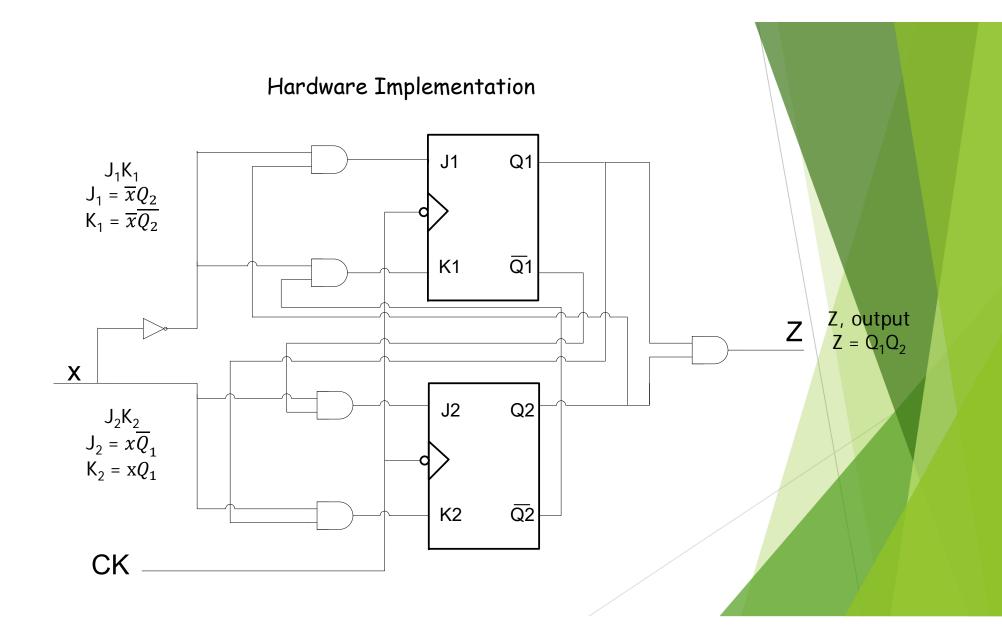

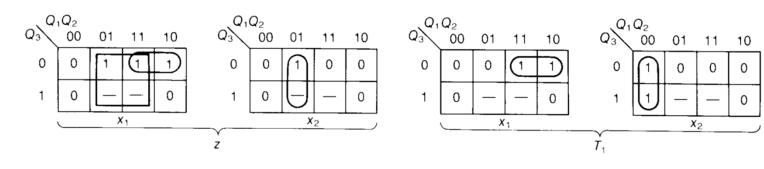

Excitation Maps and Design Equations

1

$Q_1 Q_2 00 01 11 10$

X 0 0\_ 1\_ \_0 \_1

0\_ 0\_ \_0 \_0

$J_1 K_1$  $J_1 = \overline{x} Q_2$  $K_1 = \overline{x} \overline{Q_2}$

| Q1C                                            | $\frac{00}{2}$ | 01 | 11 | 10 |  |

|------------------------------------------------|----------------|----|----|----|--|

| X<br>O                                         | 0              | 0  | 1  | 0  |  |

| 1                                              | 0              | 0  | 1  | 0  |  |

| Z, output<br>Z = Q <sub>1</sub> Q <sub>2</sub> |                |    |    |    |  |

| Q <sub>1</sub> Q |    | 01                                   |                                           |    |   |

|------------------|----|--------------------------------------|-------------------------------------------|----|---|

| Х<br>О           | 0_ | _0                                   | _0                                        | 0_ |   |

| 1                | 1_ |                                      | _1                                        |    | / |

|                  |    | J <sub>2</sub>                       | K <sub>2</sub>                            |    |   |

|                  |    | J <sub>2</sub> =<br>K <sub>2</sub> = | $     x \overline{Q}_{1} \\     x Q_{1} $ |    |   |

|                  |    |                                      |                                           |    |   |

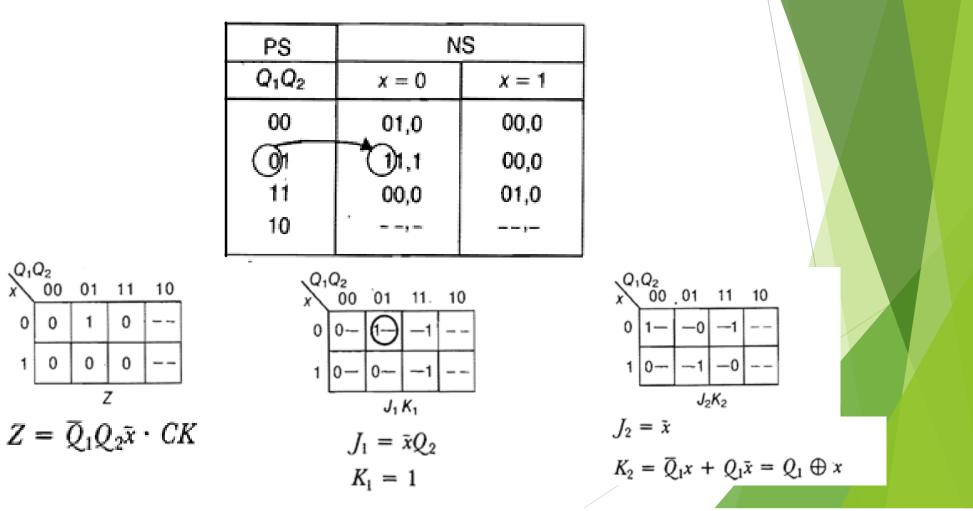

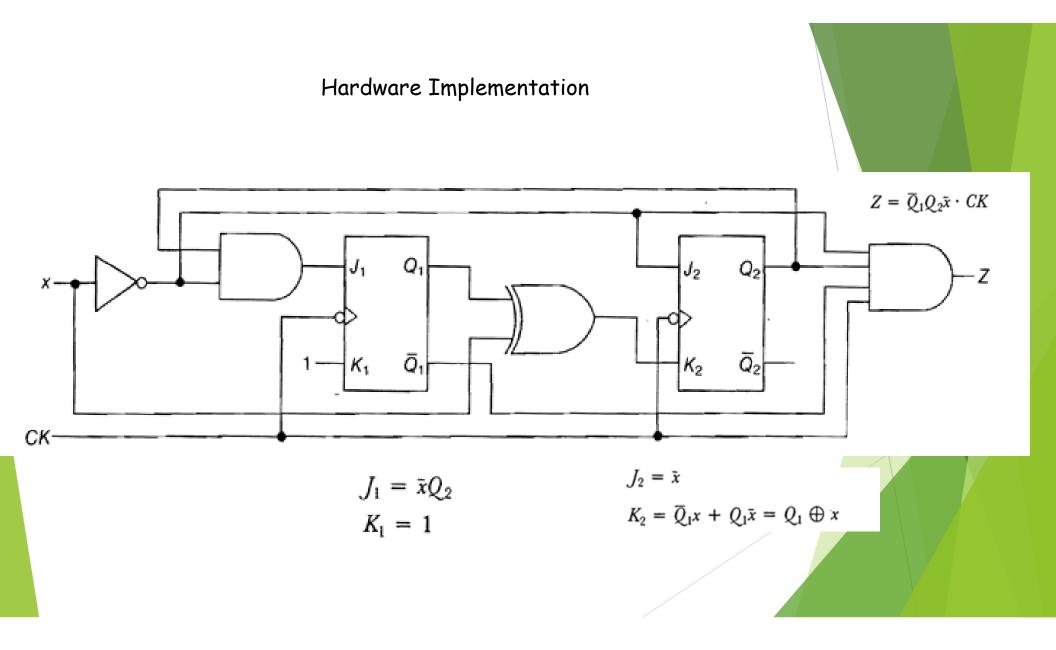

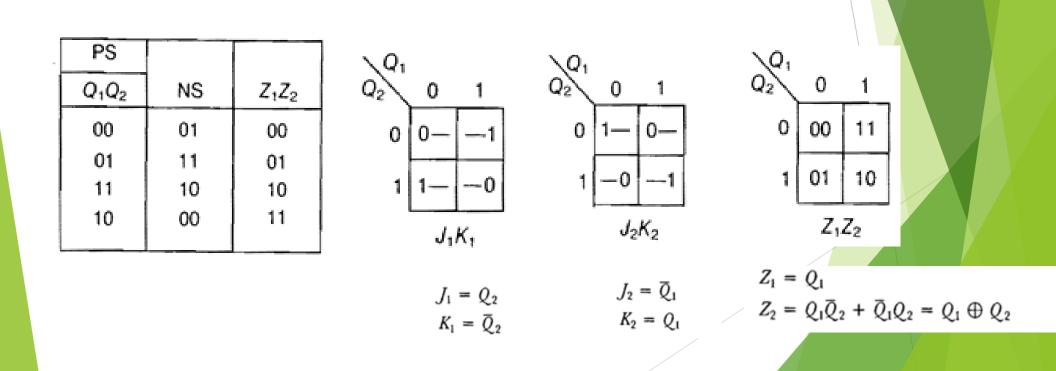

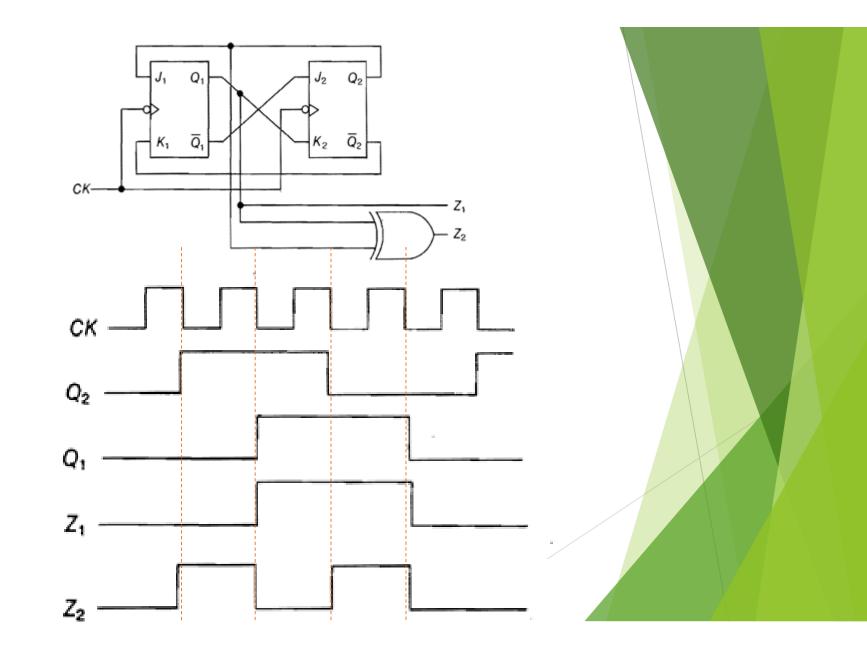

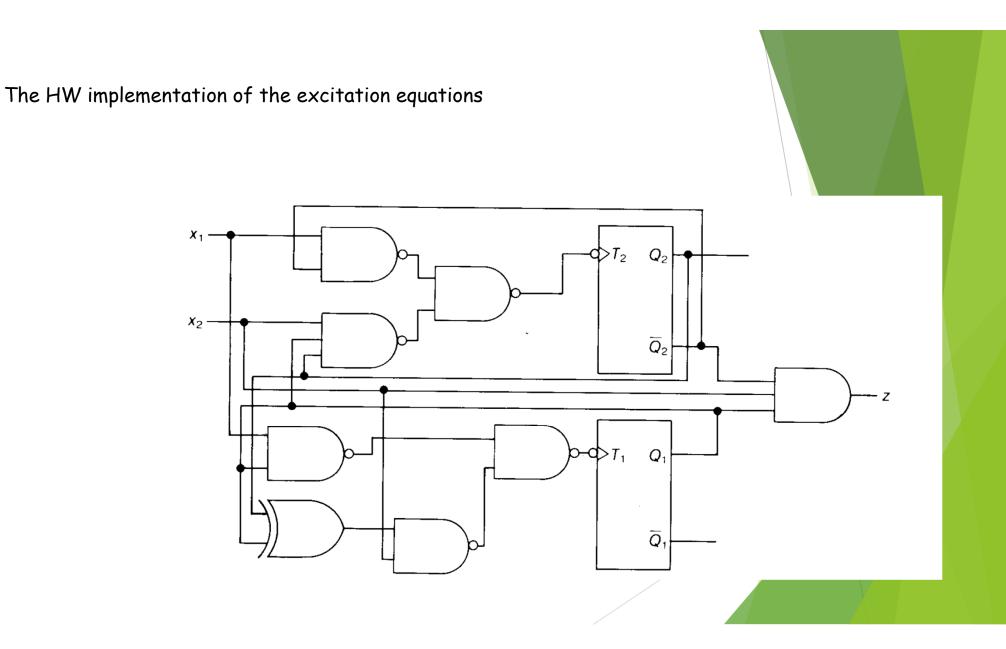

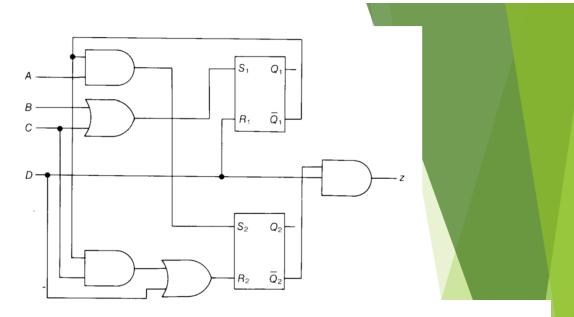

Example: Find the HW implementation of the FSM whose state transition table is given below

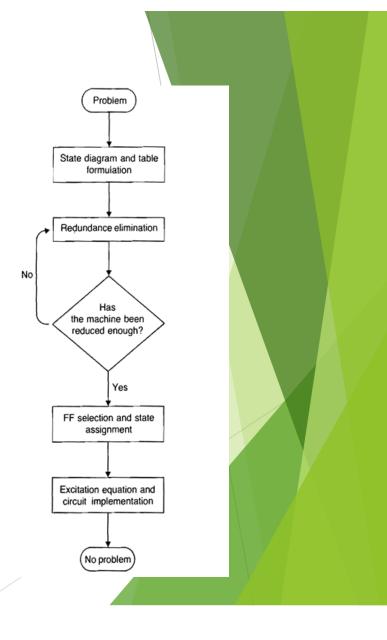

### Design Algorithm

Step 1. Obtain the state diagram from the word statement of the problem.

Step 2. Obtain the state table from the state diagram.

Step 3. Eliminate the redundant states.

Step 4. Make state assignments.

Step 5. Determine the type of FFs to use and obtain the corresponding excitation maps.

Step 6. Determine the output and FF equations.

Step 7. Construct the logic circuit.

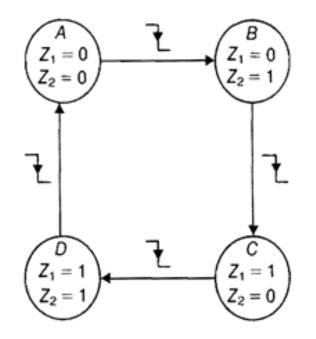

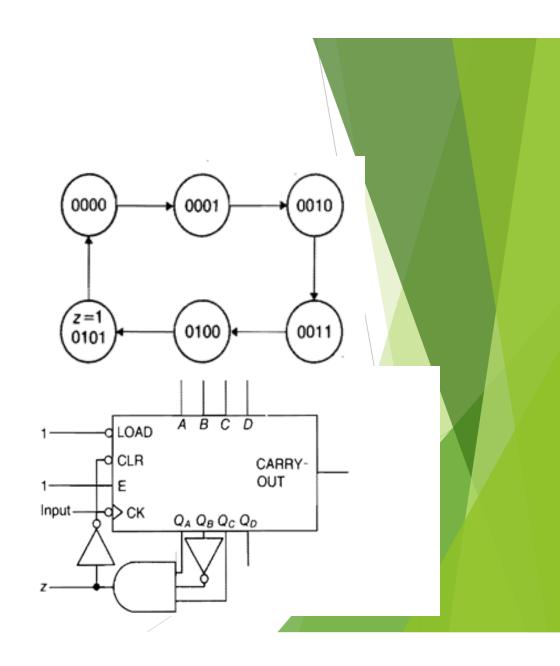

Design a two-bit clocked sequential counter circuit that counts clock pulses.

| PS | NS | $Z_1Z_2$ |

|----|----|----------|

| А  | в  | 00       |

| В  | С  | 01       |

| С  | D  | 10       |

| D  | .A | 11       |

|    |    |          |

| PS   |    |      |

|------|----|------|

| Q1Q2 | NS | Z1Z2 |

| 00   | 01 | 00   |

| 01   | 10 | 01   |

| 10   | 11 | 10   |

| 11   | 00 | 11   |

|      |    |      |

СК

1

1--

Repeat the design of Example 7.5 by assigning A = 00, B = 01, C= 11, and D = 10. Construct the corresponding timing diagram as well.

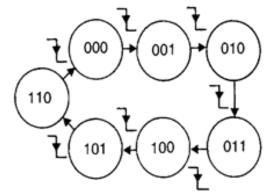

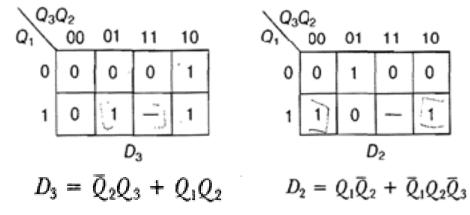

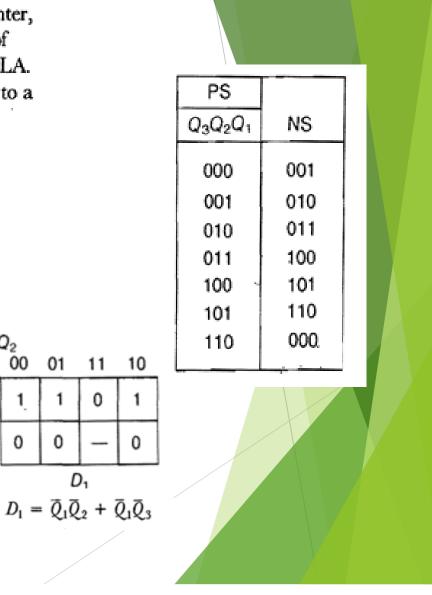

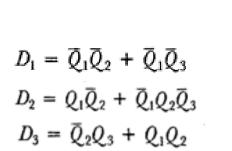

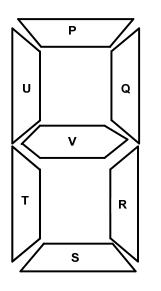

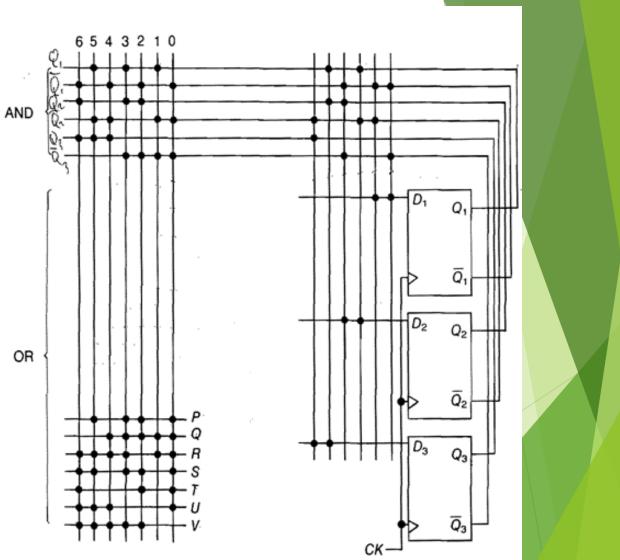

Obtain a scale-of-seven up-counter, as shown in the state diagram of Figure 7.31, using D FFs and PLA. Assume that the counter is tied to a seven-segment display device.

10

0

1

0

$Q_3Q_2$

0

1

00

0

$Q_1$

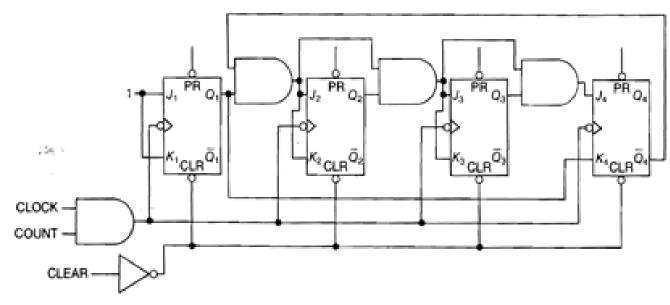

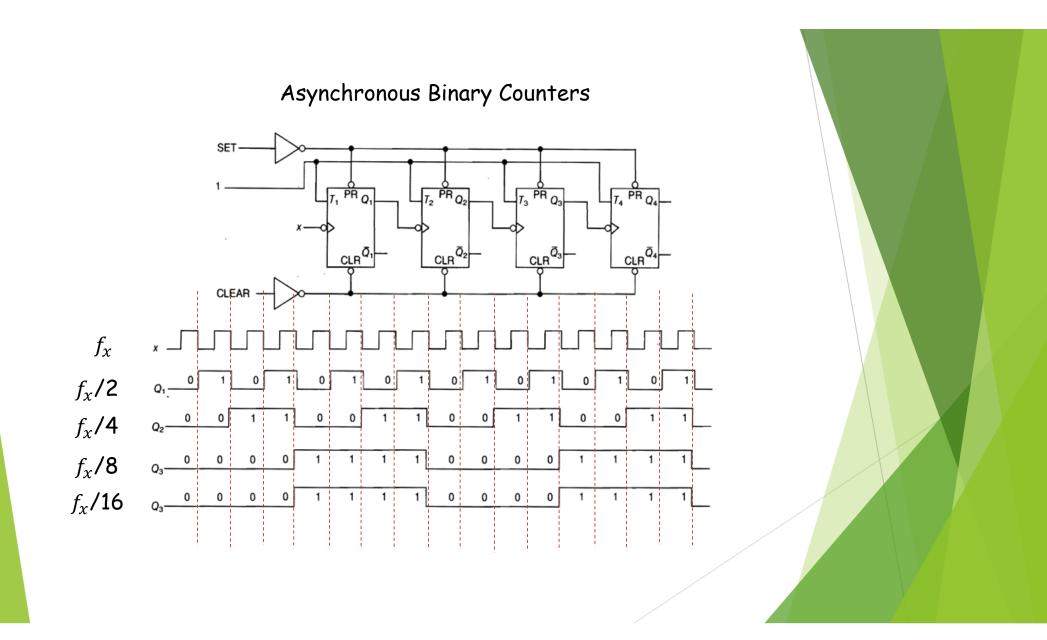

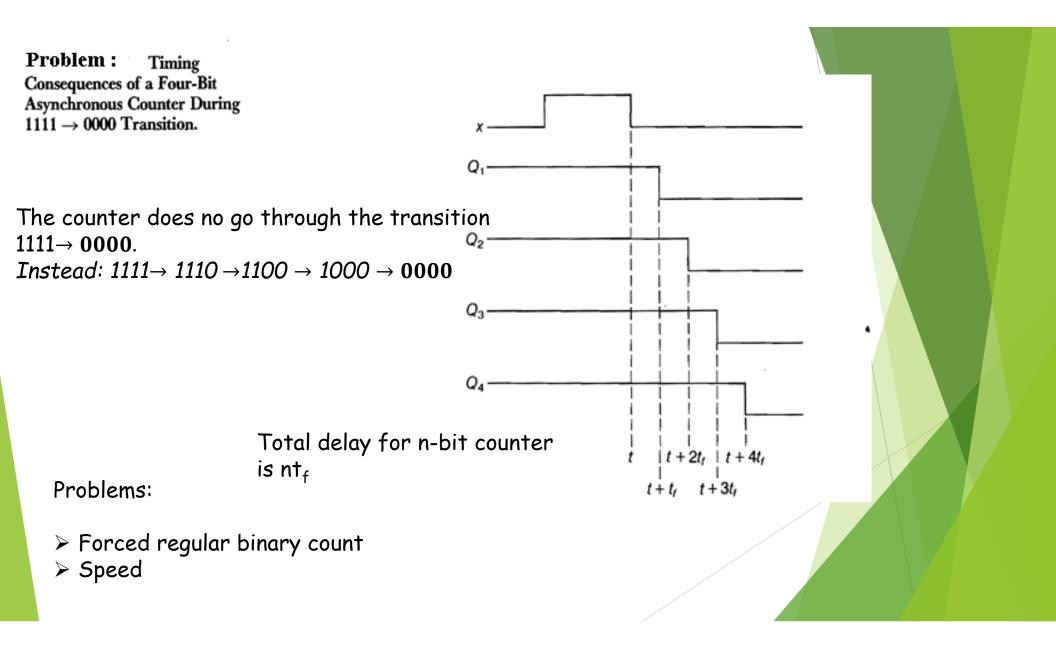

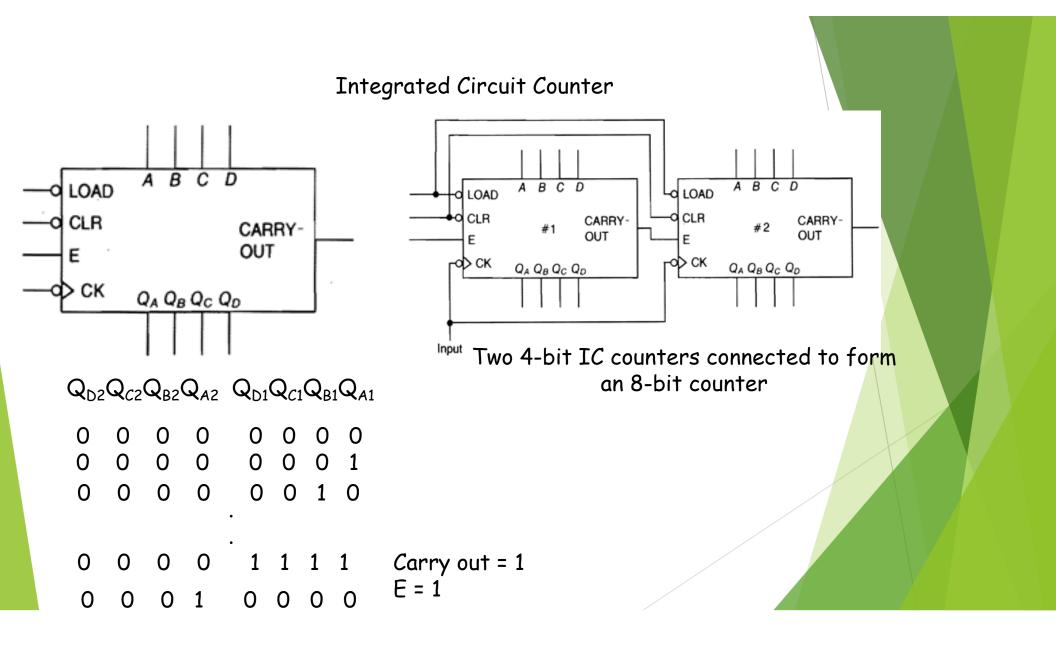

## Chapter 5: Introduction to Counters and Registers

> A unit for data manipulation \_\_\_\_\_\_ REGISTERS and logic circuits

> A second unit for regulating events of the first unit \_\_\_\_\_\_ COUNTERS

#### **Counters**:

- Synchronous

- Asynchronous

### **Registers**:

- Serial

- Parallel

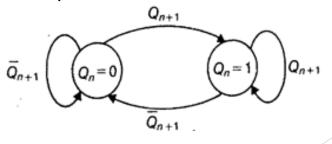

Single-bit counter

$$(0, 1, 0, 1, ...)$$

$J = K = 1$ Two-bit counter $(00, 01, 10, 11, 00, ....)$  $J_1 = K_1 = 1$  $J_2 = K_2 = Q_1$

Likewise for three-bit counter

$$J_{1} = K_{1} = 1$$

$$J_{2} = K_{2} = Q_{1}$$

$$J_{3} = K_{3} = Q_{2}Q_{1}$$

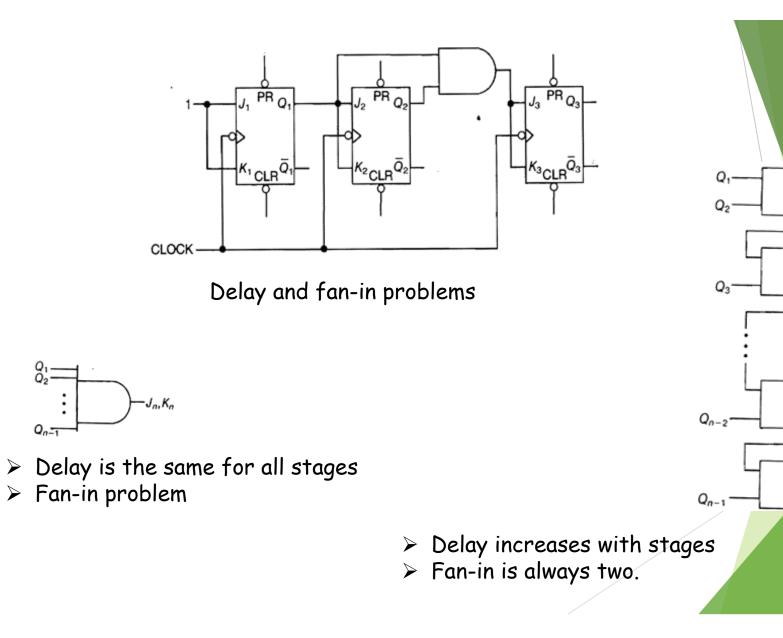

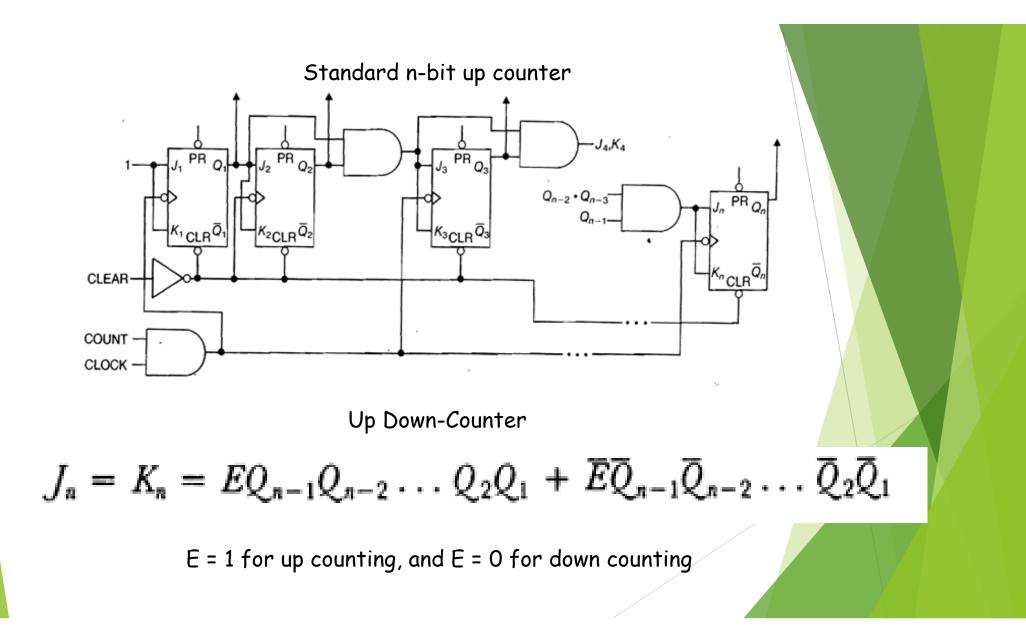

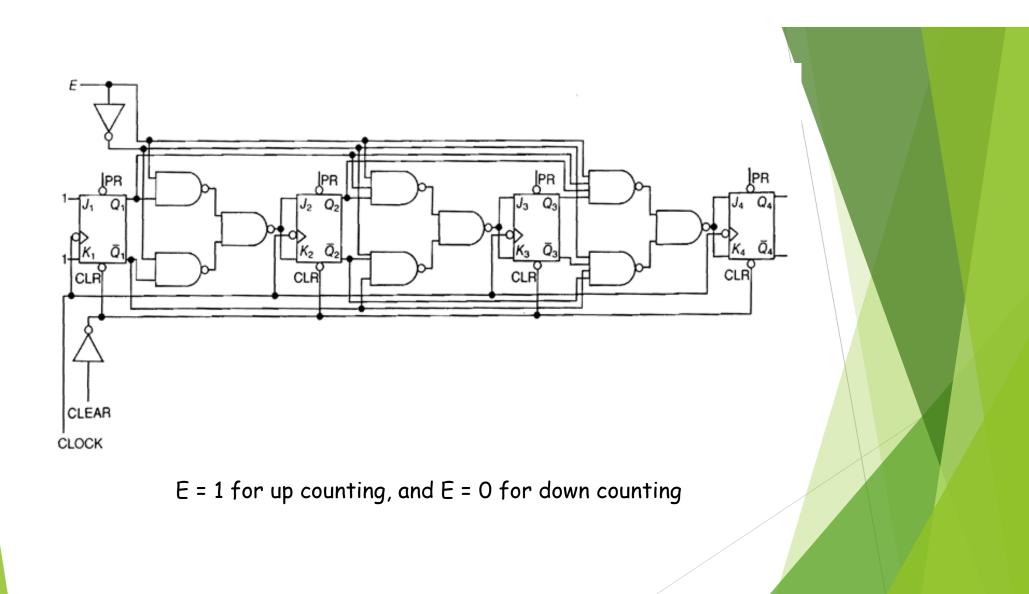

For n-bit counter

$$J_n = Q_{n-1}Q_{n-2} \dots Q_3Q_2Q_1 = Q_{n-1}J_{n-1}$$

$$K_n = Q_{n-1}Q_{n-2} \dots Q_3Q_2Q_1 = Q_{n-1}K_{n-1}$$

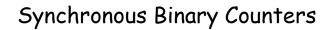

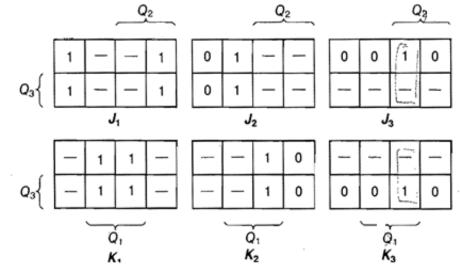

### Design a three-bit counter

| PS                |     |

|-------------------|-----|

| $Q_{3}Q_{2}Q_{1}$ | NS  |

| 000               | 001 |

| 001               | 010 |

| 010               | 011 |

| 011               | 100 |

| 100               | 101 |

| 101               | 110 |

| 110               | 111 |

| 111               | 000 |

$J_{1} = K_{1} = 1$   $J_{2} = K_{2} = Q_{1}$  $J_{3} = K_{3} = Q_{2}Q_{1}$

- J<sub>3</sub>,K<sub>3</sub>

- J4, K4

$J_{n-1}, K_n$

$J_n, K_n$

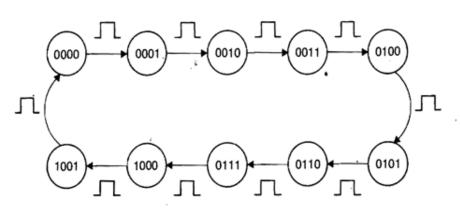

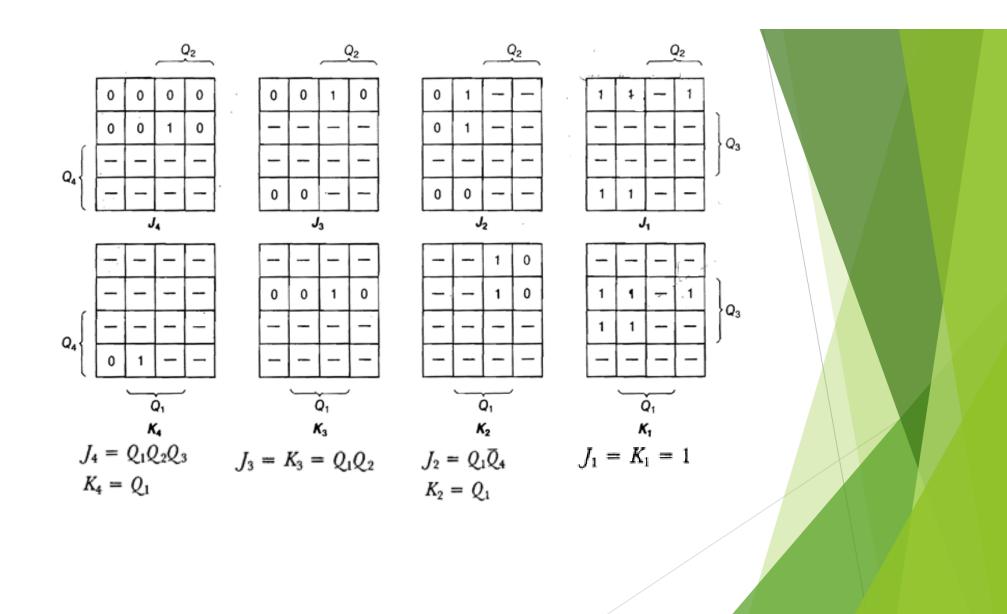

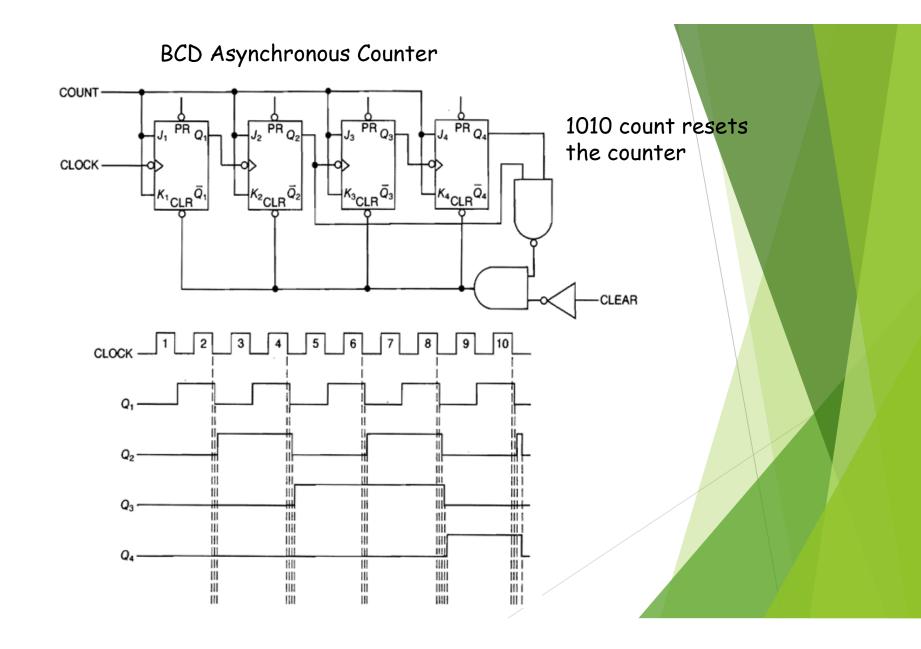

## Obtain the J and K equations for a BCD up-counter.

| PS                |      |          |          |                               |          |

|-------------------|------|----------|----------|-------------------------------|----------|

| $Q_4 Q_3 Q_2 Q_1$ | NS   | $J_4K_4$ | $J_3K_3$ | J <sub>2</sub> K <sub>2</sub> | $J_1K_1$ |

| 0000              | 0001 | 0-       | 0-       | 0-                            | 1        |

| 0001              | 0010 | 0-       | 0        | 1—                            | -1       |

| 0010              | 0011 | 0-       | 0-       | -0                            | 1—       |

| 0011              | 0100 | 0-       | 1—       | - 1                           | -1       |

| 0100              | 0101 | 0-       | -0       | 0                             | 1        |

| 0101              | 0110 | 0-       | 0        | 1-                            | -1       |

| 0110              | 0111 | 0-       | -0       | 0                             | 1—       |

| 0111              | 1000 | 1-       | -1       | -1                            | -1       |

| 1000              | 1001 | 0        | 0-       | 0-                            | 1—       |

| 1001              | 0000 | 1        | 0-       | 0 —                           | 1        |

From a regular 4-bit counter the BCD one Can be thought of as such:

1001 should switch to0000 and not to1010

$Q_4$ , the MSB, should become a 0,  $Q_2$  should be prevented from becoming a 1.

$Q_1$  should be fed to  $K_4$ ,  $K_4$  and  $J_4$  should not be connected,  $Q_1\overline{Q}_4$  should be fed to  $J_2$  and  $K_2$ . Obtain the state table for the counter shown in Figure 10.10, starting from the count 000. The MSB of the count is at  $Q_3$ .

$$J_{1} = \overline{Q_{3}}, \qquad K_{1} = Q_{2}$$

$$J_{2} = Q_{1} + Q_{3} \qquad K_{2} = 1$$

$$J_{3} = K_{3} = Q_{2}$$

0, 1, 3, 4, 6, 0, .....

|   |                                                                 |     |    |    |    | ous count              |   |                  |             |                   | PS          | NS         |          |   |        |                |    | }  |  |

|---|-----------------------------------------------------------------|-----|----|----|----|------------------------|---|------------------|-------------|-------------------|-------------|------------|----------|---|--------|----------------|----|----|--|

|   | produces the count sequence 0, 2, 4,<br>3, 6, 7, 0, $J_1 = Q_3$ |     |    |    |    |                        |   |                  | $Q_3Q_2Q_1$ | $Q_{3}Q_{2}Q_{1}$ | $J_3K_3$    |            | $J_2K_2$ | J | 1K1    |                |    |    |  |

| 5 | , 0, 1                                                          | , v | ,  | •• |    | $J_1 = Q_3$            |   |                  |             |                   | 000         | 010        | 0        | - | 1      | 0              | ·  |    |  |

|   |                                                                 |     |    |    |    | $K_1 = 1$              |   |                  |             |                   | 001         |            |          | - |        | _              |    |    |  |

|   |                                                                 |     |    |    |    | $J_2 = 1$              |   |                  |             |                   | 010         | 100        | 1—       |   | —1     | 0              |    |    |  |

|   |                                                                 |     |    |    |    | $K_2 = \overline{Q_1}$ | Ð | $\overline{Q_3}$ |             |                   | .011<br>100 | 110<br>011 | 1—-<br>1 |   | Q<br>1 |                | 1  |    |  |

|   |                                                                 |     |    |    |    | $J_3 = Q_2$            |   |                  |             |                   | 100         |            |          | - |        |                |    |    |  |

|   |                                                                 |     |    |    |    | $K_3 = Q_1$            |   | ō.               |             |                   | 110         | 111        | 0        |   | -0     | 1              |    |    |  |

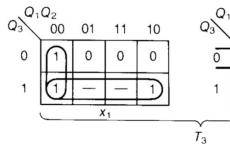

| ( | $Q_2Q_1$                                                        |     |    |    |    | 113 - QI               |   | ×2               |             |                   | 111         | 000        | 1        |   | —1     | _              | -1 |    |  |

|   | $Q_3$                                                           | 00  | 01 | 11 | 10 |                        |   | 00               | 01          | 11                | 10          |            |          |   | 00     | 01             | 11 | 10 |  |

|   | 0                                                               | 0   | -  | -  | 0  |                        | 0 | 1                | -           | -                 | -           |            |          | 0 | 0      | -              | 1  | 1  |  |

|   | 1                                                               | 1   | -  | -  | 1  |                        | 1 | 1                | -           | -                 | -           |            |          | 1 | -      | -              | -  | -  |  |

|   | $Q_2Q_1$                                                        |     | J  | 1  |    |                        |   |                  | $J_2$       | 2                 |             |            |          |   |        | $\mathbf{J}_3$ | 3  |    |  |

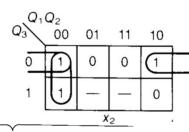

|   | $Q_3$                                                           | 00  | 01 | 11 | 10 |                        |   | 00               | 01          | 11                | 10          |            |          |   | 00     | 01             | 11 | 10 |  |

|   | 0                                                               | -   | -  | 1  | -  |                        | 0 | -                | -           | 0                 | 1           |            |          | 0 | -      | -              | -  | -  |  |

|   | 1                                                               | -   | -  | 1  | -  |                        | 1 | -                | -           | 1                 | 0           |            |          | 1 | 1      | -              | 1  | 0  |  |

|   |                                                                 |     | K  | 1  |    |                        |   |                  | K           | 2                 |             |            |          |   |        | K              | 3  |    |  |

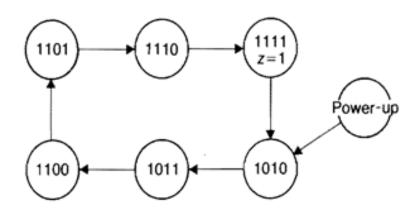

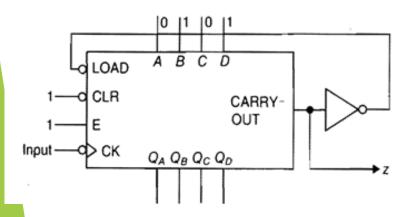

Design a counter using the module of Figure 10.18 that outputs a 1 each time six counts have been received.

# The END

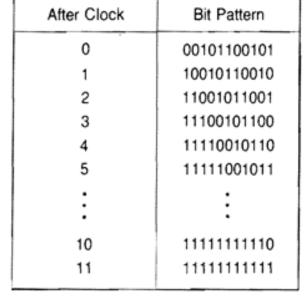

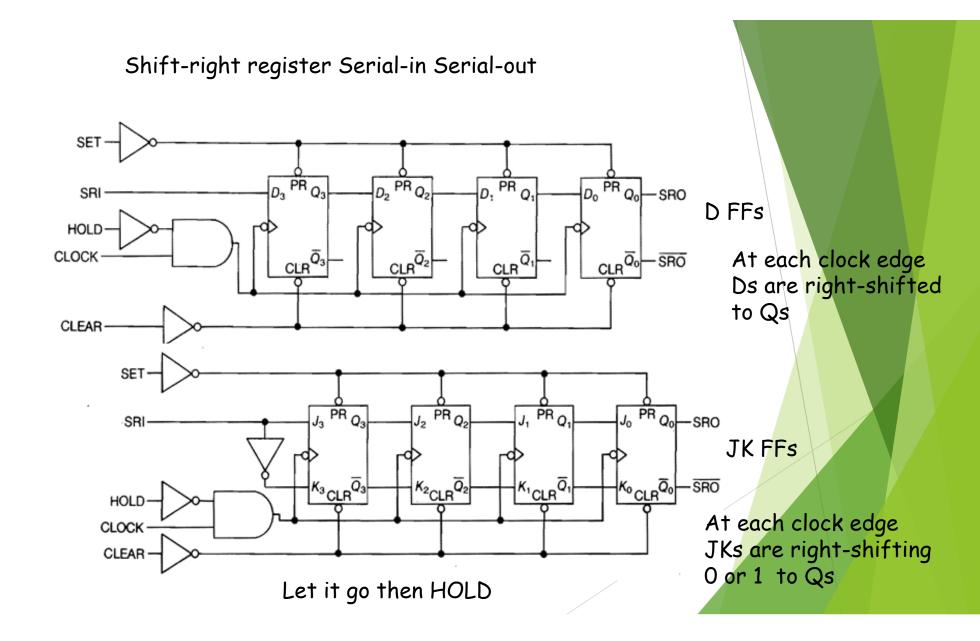

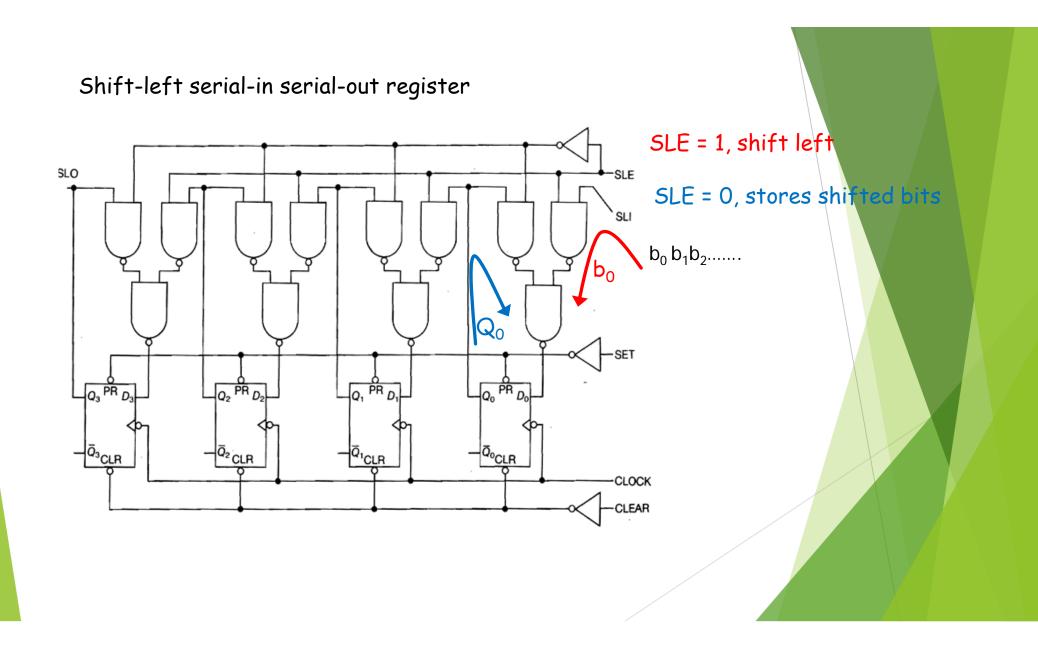

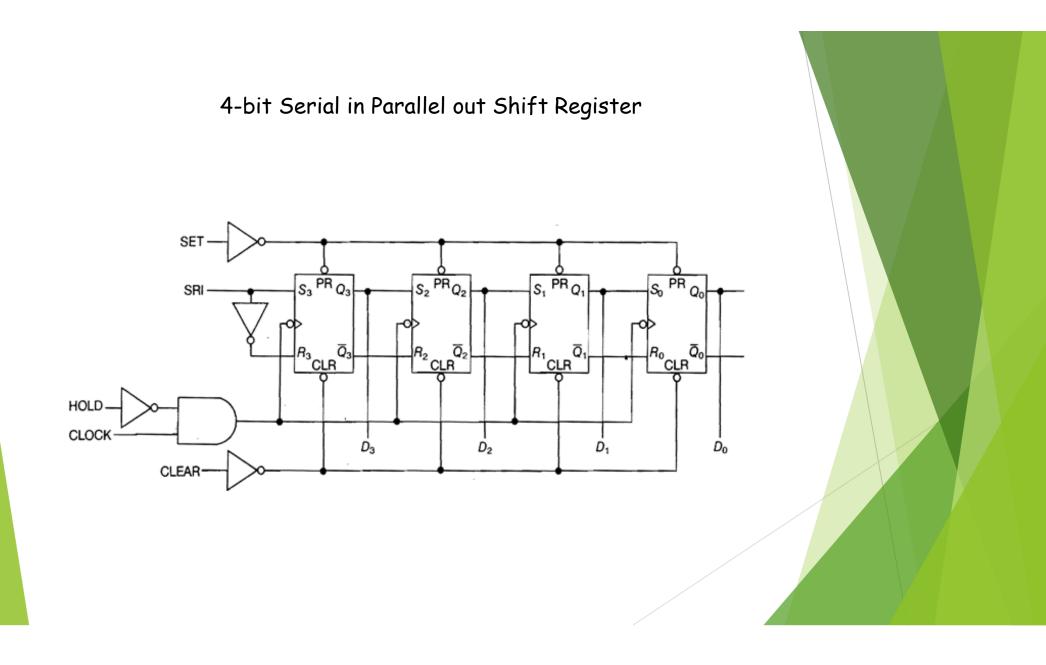

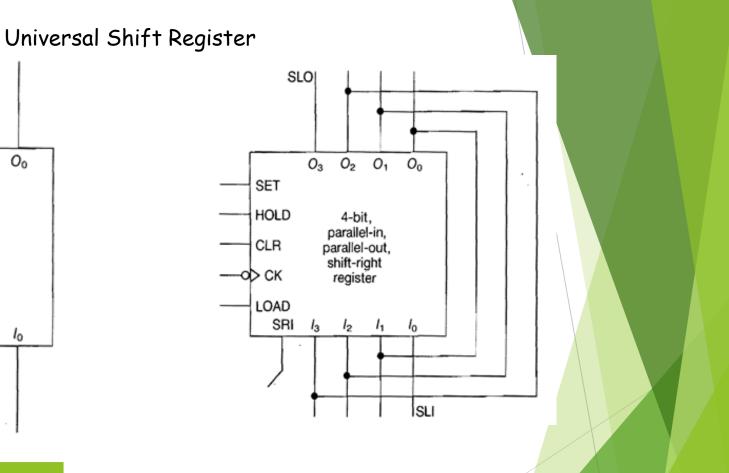

### The Basic Shift Reregister

| LSBs are lost and MSBs are replaced with ones<br>Shift-right register |

|-----------------------------------------------------------------------|

| LSBs replace MSBs<br>Circulate-right register                         |

| MSBs replace LSBs<br>Circulate-left register                          |

| Shift left one bit = multiply by 2                                    |

Shift right one bit = divide by 2

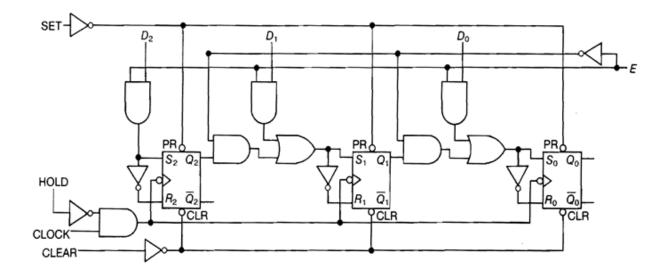

3-bit parallel in serial out shift register

| E | Action      |

|---|-------------|

| 1 | Data loaded |

| 0 | Right-shift |

| Hold | Action        |

|------|---------------|

| 0    | Load or shift |

| 1    | Restores      |

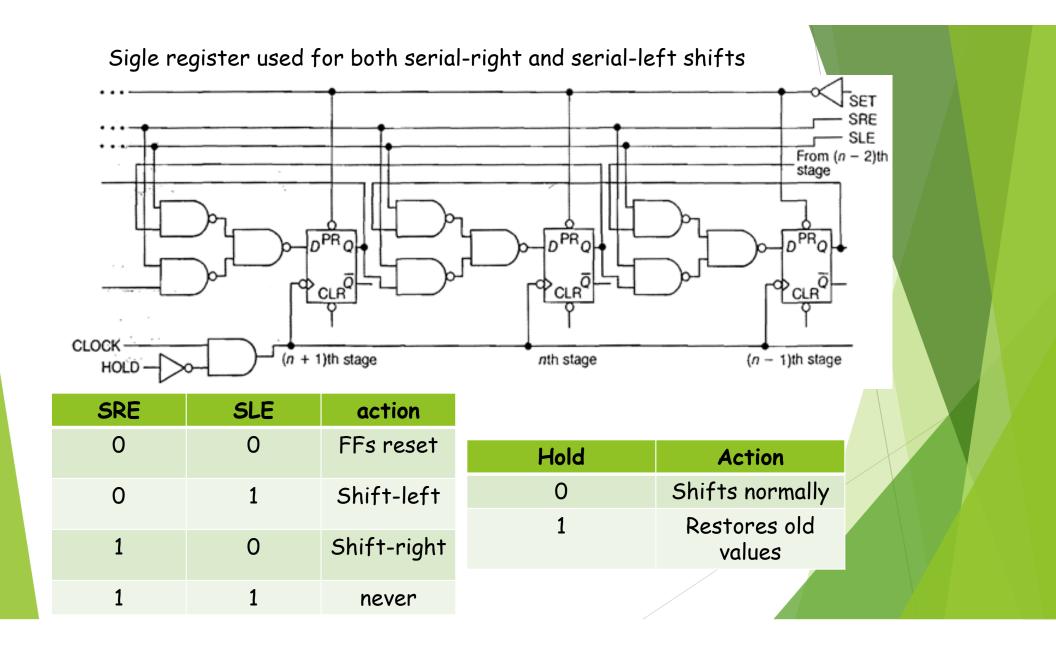

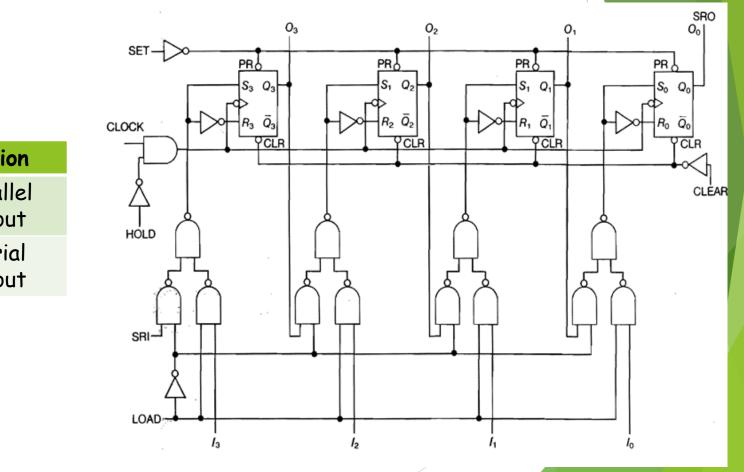

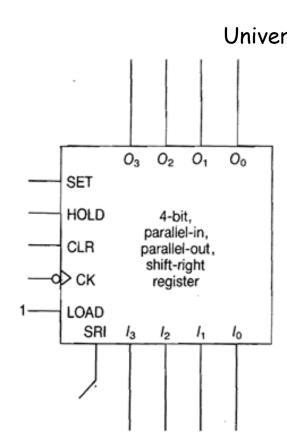

### 4-bit Parallel in Parallel out Shift Register

| Load | Action             |

|------|--------------------|

| 1    | Parallel<br>in/out |

| 0    | Serial<br>in/out   |

| Load | Action                       |

|------|------------------------------|

| 0    | Shift-right<br>serial in/out |

| 1    | Parallel                     |

Wired shift-left register

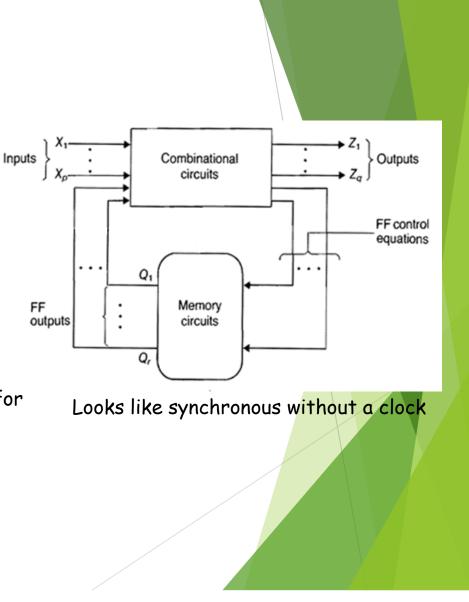

### Chapter 5: Design of Asynchronous Sequential Circuits

## Pulse-Mode Circuits:

No clock for state transitions.

Just input pulses, Key boards and Vending machines

No overlapping pulses

Conditions for perfect circuit operation

- 1. Simultaneous input pulses on two or more lines are forbidden. Interval between pulses is large enough for system to return to a stable state.

- 2. Pulse widths must be sufficient to allow the components to respond to them.

As long as the previously stated two conditions are met the design of asynchronous circuits will be similar to the synchronous ones

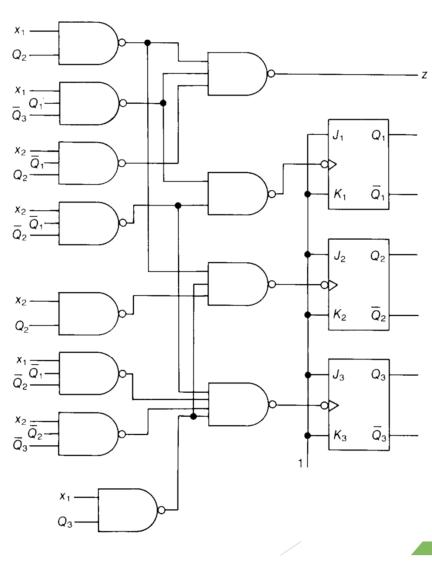

x3 x2 An example of three nonoverlapping input pulses x1 Design Algorithm 1. Get the state diagram. For n-inputs there be n transition paths leaving each of the sates. 2. Remove redundancies. 3. Assign states and generate state transition 4. Get the excitation maps and write down the

excitation equations.

table.

5. Draw the circuit diagram.

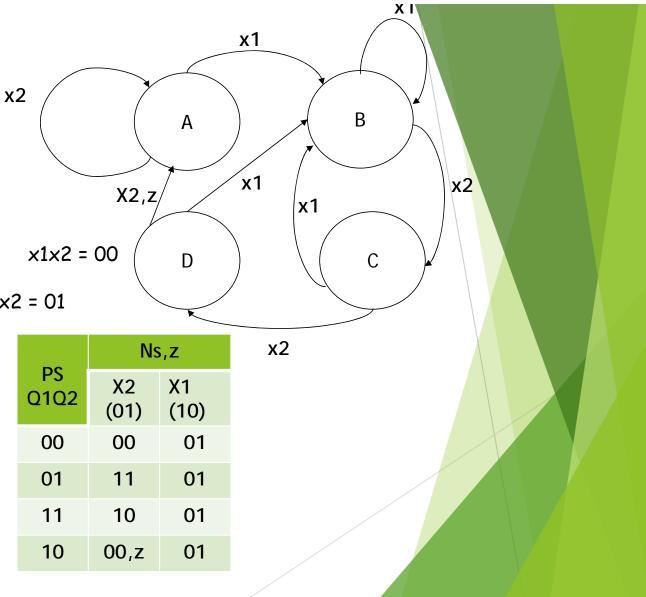

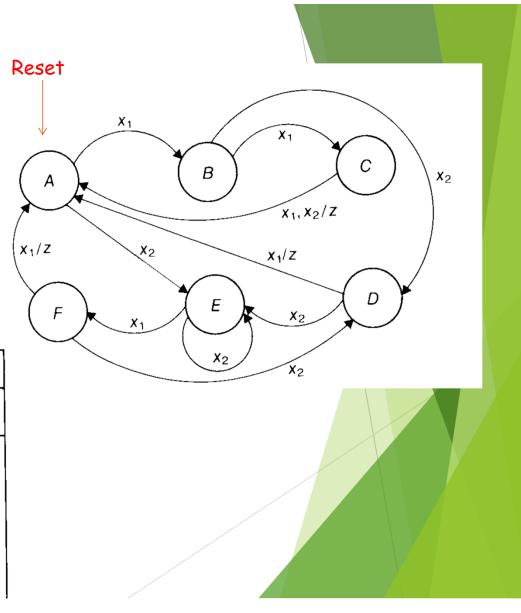

Example: Design a circuit that receives two inputs x1 and x2 and gives an output coincident with the third consecutive x2 pulse following at least one x1 pulse.

Forbidden pulses: x1x2 = 11

No pulses have occured

Useful pulses x1x2 = 10 and x1x2 = 01

|    | Ns,z |    |  |  |

|----|------|----|--|--|

| PS | x2   | x1 |  |  |

| Α  | А    | В  |  |  |

| В  | С    | В  |  |  |

| С  | D    | В  |  |  |

| D  | A,z  | В  |  |  |

|                 |              |               |         |      |                    |    | PS<br>Q1Q2 | N<br>X2<br>(01) | ls,z<br>X1<br>(10) |                |  |  |

|-----------------|--------------|---------------|---------|------|--------------------|----|------------|-----------------|--------------------|----------------|--|--|

|                 |              |               |         |      |                    |    | 00         | 00              | 01                 |                |  |  |

|                 |              |               |         |      |                    |    | 01         | 11              | 01                 |                |  |  |

| Excita<br>T FFs |              | aps:<br>sumed |         |      |                    |    | 11         | 10              | 01                 |                |  |  |

| 1     5         |              | Sumea         |         |      |                    |    | 10         | 00,z            | 01                 |                |  |  |

| Q1Q2            | x1           | x2            |         | Q1Q2 | x1                 | x  | 2          | Q1Q             | 2 x1               | x2             |  |  |

| 00              | 0            | 0             |         | 00   | 1                  | C  | )          | 00              | 0                  | 0              |  |  |

| 01              | 0            | 1             |         | 01   | 0                  | C  | )          | 01              | 0                  | 0              |  |  |

| 11              | 1            | 0             |         | 11   | 0                  | 1  |            | 11              | 0                  | 0              |  |  |

| 10              | 1            | 1             |         | 10   | 1                  | C  | )          | 10              | 0                  | 1              |  |  |

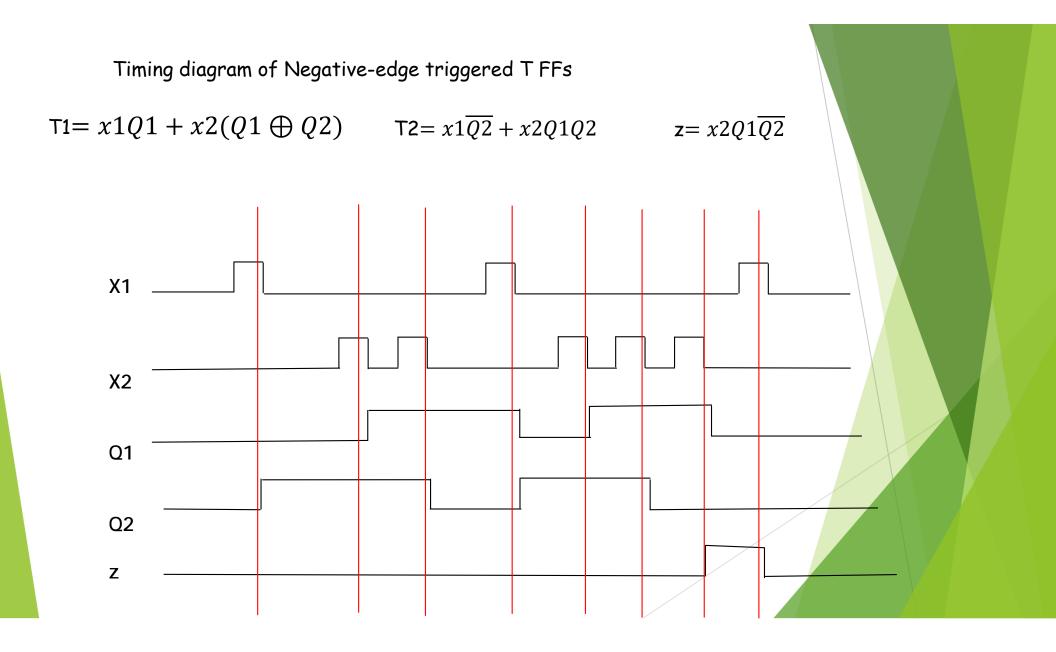

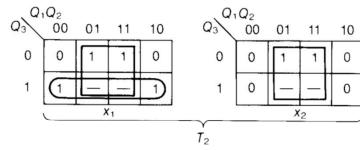

| T1 = x1Q        | <u>)</u> 1+. | x2(Q1         | . ⊕ Q2) | T2=  | $= x1\overline{Q}$ | 2+ | x2Q1Q2     | 2               | z= :               | x2Q1 <u>Q2</u> |  |  |

## Example 2:

Design a pulse-mode circuit that satisfies the following requirements. The circuit has two inputs,  $x_1$  and  $x_2$ , and one output, z. The output pulse is to be produced simultaneously with the last of a sequence of three input pulses if and only if the sequence contained at least two  $x_1$ pulses. After each output a new sequence is looked for.

|    | NS                    | S, z                  |

|----|-----------------------|-----------------------|

| PS | <i>x</i> <sub>1</sub> | <b>x</b> <sub>2</sub> |

| A  | В                     | E                     |

| В  | С                     | D                     |

| С  | A,z                   | A,z                   |

| D  | A,z                   | E                     |

| E  | F                     | E                     |

| F  | A,z                   | D                     |

No redundance states

Implication table

Arbitrary state assignment

$\mathbf{x}_2$

Ε

D

A,z

Ε

E

D

| PS            | NS, z          |                       |  |  |

|---------------|----------------|-----------------------|--|--|

| $Q_1 Q_2 Q_3$ | X <sub>1</sub> | <b>x</b> <sub>2</sub> |  |  |

| 000           | 001            | 101                   |  |  |

| 001           | 010            | 100                   |  |  |

| 010           | 000, <i>z</i>  | 000, <i>z</i>         |  |  |

| 100           | 000, <i>z</i>  | 101                   |  |  |

| 101           | 110            | 101                   |  |  |

| 110           | 000, <i>z</i>  | 100                   |  |  |

$$z = x_1(Q_2 + Q_1 \overline{Q}_3) + x_2(\overline{Q}_1 Q_2)$$

$$T_1 = x_1(Q_1 \overline{Q}_3) + x_2(\overline{Q}_1 \overline{Q}_2)$$

$$T_2 = x_1(Q_2 + Q_3) + x_2(Q_2)$$

$$T_3 = x_1(Q_3 + \overline{Q}_1 \overline{Q}_2) + x_2(\overline{Q}_1 \overline{Q}_2 + \overline{Q}_2 \overline{Q}_3)$$

| PS            | NS, Z          |                       |  |  |  |

|---------------|----------------|-----------------------|--|--|--|

| $Q_1 Q_2 Q_3$ | Х <sub>1</sub> | <b>x</b> <sub>2</sub> |  |  |  |

| 000           | 001            | 101                   |  |  |  |

| 001           | 010            | 100                   |  |  |  |

| 010           | 000, <i>z</i>  | 000, <i>z</i>         |  |  |  |

| 100           | 000,z          | 101                   |  |  |  |

| 101           | 110            | 101                   |  |  |  |

| 110           | 000, <i>z</i>  | 100                   |  |  |  |

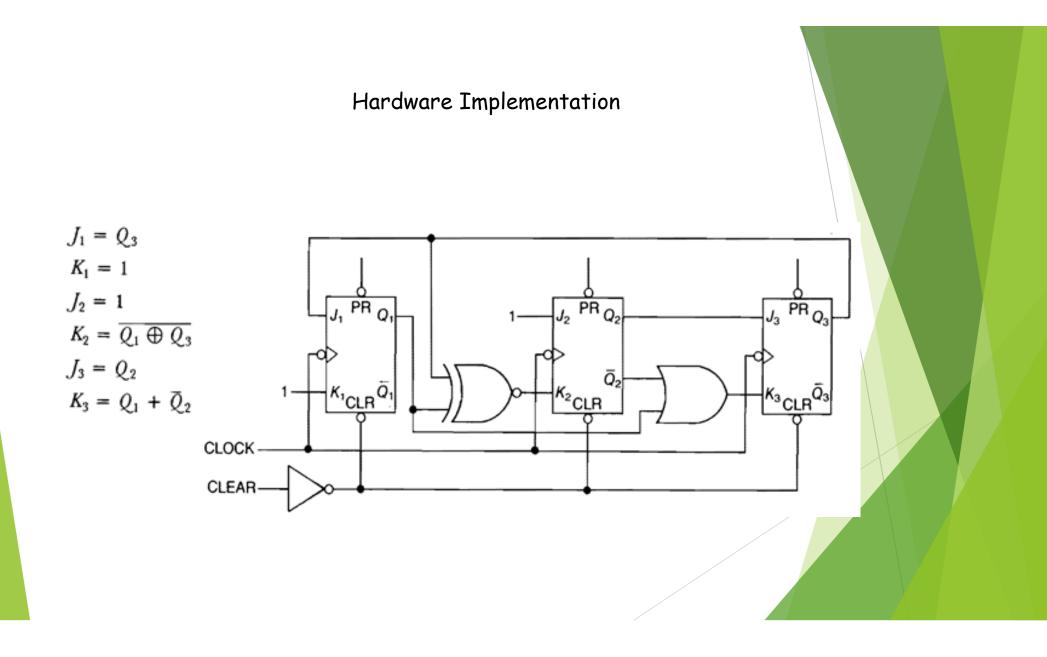

HW Implementation

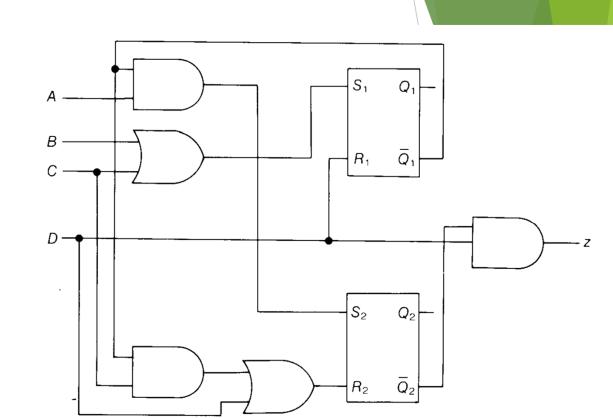

Example 3 Analyze the pulse-mode circuit of Figure

The equations of the states and the output are easily written as:

$S_{1} = B + C$   $R_{1} = D$   $S_{2} = A\overline{Q}_{1}$   $R = C\overline{Q}_{1} + D$   $Z = D\overline{Q}_{2}$

Since it is a pulse-mode circuit the only input conditions that need to be considered are ABCD = 1000, 0100, 0010, and 0001.

| PS                           | NS. z                        |                                      |                              |                              |  |  |  |  |

|------------------------------|------------------------------|--------------------------------------|------------------------------|------------------------------|--|--|--|--|

| $Q_1 Q_2$                    | А                            | В                                    | С                            | D                            |  |  |  |  |

| P 00<br>Q 01<br>R 11<br>S 10 | 01.0<br>01.0<br>11,0<br>10,0 | 10,0<br>11,0<br>11,0<br>11,0<br>10,0 | 10.0<br>10,0<br>11.0<br>10,0 | 00.1<br>00.0<br>00.0<br>00.1 |  |  |  |  |