# Lecture\_1

# Microprocessors Systems

**CSE 238**

Prof. M. E I-Banna

## CSE 238 ILOs

### ILO # Description

- 1 Understand the general working of computers.

- 2 Comprehend the internal structure of computers, CPU, memory and buses.

- 3 Comprehend the concept of pipelining and pre-fetch queue.

- Know the 8088/8086 internal four types of registers, general purpose, index and pointers, segment,

- 4 as well as flag registers.

- Differentiate between logical and physical memory in accordance to the memory structure of 8086/

- 5 8088 Intel's processors.

- 6 Define different memory segments in Intel's 8086/8088 processors.

- 7 Know the different addressing modes of Intel's processors.

## CSE 238 ILOs

#### ILO#

### **Description**

- 9 Comprehend and use the instruction set of 8086/8088 processors.

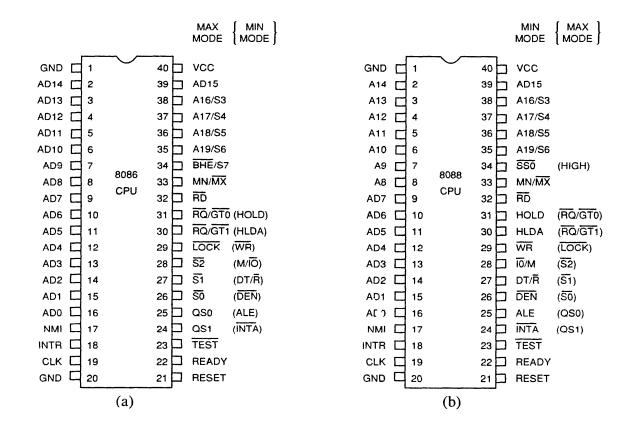

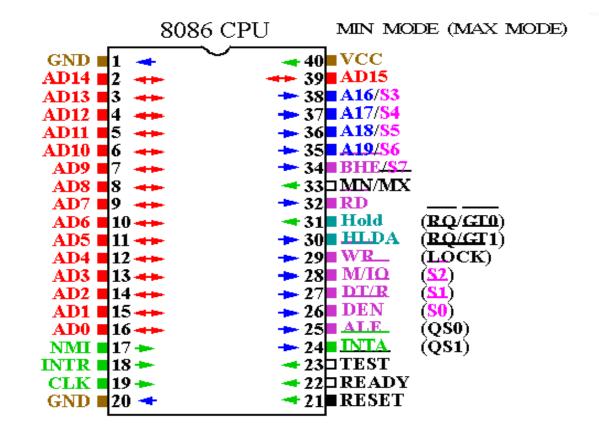

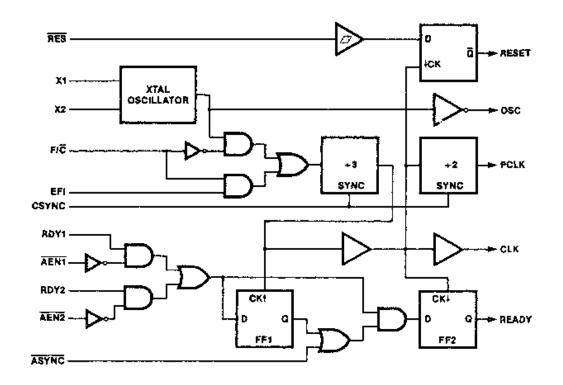

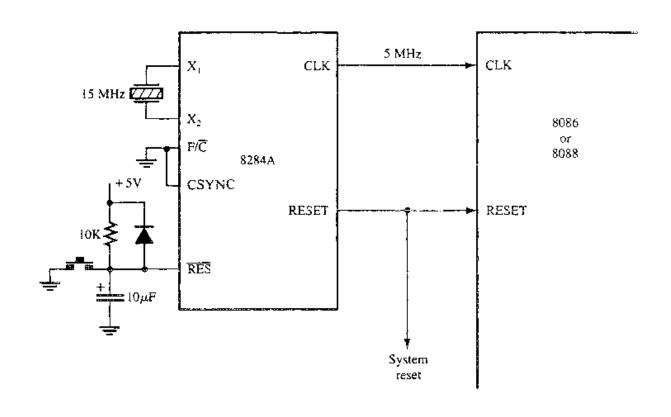

- **10** Hardware specifications and pin configuration of Intel's 8086/8088 microprocessors

- 11 Understand how memory and I/O ports can be interfaced with microprocessors.

- Use a microprocessor kit to exercise the above gained skills by writing assembly codes to drive and test different operations.

#### Microprocessors Systems CSE 238

Term: Spring 2024

Instructors: Dr. M. El-Banna, Room: 4th floor EE-Building

Dr. Hania Farag, Room: 3rd floor EE Building

Classes: G3 and G4 Dr. Banna MON 02:00 - 04:40 G4 K5

TUE 11:10 - 02:50 G3 K5

Office Hours: Monday 12:00-02:00

Tuesday 10:00 – 11:00

Thursday 10:00 – 12:00

Lab TAs: Eng. A. Shasly and TBD

Topics to be covered:

#### Software

Chapter 1: General knowledge of computers

Chapter 2: Introduction to the Intel's 8086/8088 microprocessor

Chapter 3: Addressing Modes

Chapter 4: Data movement instructions

Chapter 5: Logical and arithmetic instructions.

Chapter 6: machine coding

Chapter 7: Program control instructions

#### Hardware

Chapter 1: Hardware specifications of 8086/8088

Chapter 2: Memory Interfacina

### Microprocessors Systems CSE 238

Text Book: The INTEL Microprocessors, Eighth Edition Barry B. Brey

### **Grading Policy:**

Midterm 30%

LAB 20%

Tutorials attendance/Quizzes 10% (5% +5%)

Final 40%

#### Microprocessors Systems CSE 238

### Useful Codes and links:

Course code: 9dlbhy3

Website: http://eng.staff.alexu.edu.eg/staff/mbanna/public\_html/

Youtube channel: "BannaElectronics"

https://www.youtube.com/channel/UCaKy\_YOLJaPieD4ve59LZEQ/playlists

## General Knowledge of Computers

What is a computer composed of?

1. CPU

2. Memory

3. I/O devices

### The CPU connects with

- 1. Memory (RAM, ROM, and HD)

- 2. I/O devices (KB, Printers, and Monitor)

## Using 1. Address Bus

- 2. Data bus

- 3. Control Bus

What is The CPU composed of?

1. Registers

2. Arithmetic Logic Unit

3. Program Counter

4. Instruction Decoder

What is a Microprocessor?

# All four CPU components integrated into a single chip called a microprocessor in 1971

## CISC Vs RISC

#### **CISC**

- 1. Large number of instructions

- 2. Different lengths

- 3. Multiple cycles

- 4. Complex operations

- 5. Interfaced Memory

#### **RISC**

Small number of instructions

Fixed lengths

Single cycle

Simple operations

**Built-in Memory**

# Chapter 1: Introduction

- There are two big microprocessors families:

- Intel (80xxx).

- Motorola (68xxx).

- The Intel Microprocessors are used in the PCs.

- In this course, we study the Intel  $\mu$ Ps.

# 1.1. Evolution of the Intel's μPs.

| Product           | 8080 | 8085 | 8086  | 8088  | 80286  | 80386   | 80486       |

|-------------------|------|------|-------|-------|--------|---------|-------------|

| Year introduced   | 1974 | 1976 | 1978  | 1979  | 1982   | 1985    | 1989        |

| Clock rate (MHz)  | 2-3  | 3-8  | 5-10  | 5-10  | 6-16   | 16-33   | 25-50       |

| No. Transistors   | 4500 | 6500 | 29000 | 29000 | 130000 | 275000  | 1.2 million |

| Physical memory   | 64K  | 64K  | 1M    | 1M    | 16M    | 4G      | 4G          |

| External data bus | 8    | 8    | 16    | 8     | 16     | 32      | 32          |

| Address bus       | 16   | 16   | 20    | 20    | 24     | 32      | 32          |

| Data type (bits)  | 8    | 8    | 8,16  | 8,16  | 8,16   | 8,16,32 | 8,16,32     |

# 1.1. Evolution of the Intel's $\mu Ps.$

| Product           | P pro      | PII        | P III      | P 4        |

|-------------------|------------|------------|------------|------------|

| Year introduced   | 1995       | 1997       | 1978       | 2000       |

| Clock rate (MHz)  | 150-166    | 266-333    | 1000, 1G   | 3.2G       |

| No. Transistors   | 21M        | ?          | ?          | ?          |

| Physical memory   | 4-64G      | 64G        | 64G        | 64G        |

| External data bus | 64         | 64         | 64         | 64         |

| Address bus       | 32-36      | 36         | 36         | 36         |

| Data type (bits)  | 8,16,32,64 | 8,16,32,64 | 8,16,32,64 | 8,16,32,64 |

## 1.1. Evolution of the Intel's

# μPs.

Intel® Core™ Processors HX-Series (14th gen): SKU Comparison

| Processor Number                                  |        | Intel® Core® i9 Processor 14900HX | Intel® Core® i7 Processor 14700HX | Intel® Core® i7 Processor 14650HX | Intel® Core® i5 Processor 14500HX | Intel® Core® i5 Processor 14450HX |  |

|---------------------------------------------------|--------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|--|

| Processor Cores (P-cores + E-cores) <sup>11</sup> |        | 24 (8+16)                         | 20 (8+12)                         | 16 (8+8)                          | 14 (6+8)                          | 10 (6+4)                          |  |

| Processor Threads                                 |        | 32                                | 28                                | 24                                | 14                                | 10                                |  |

| Intel® Smart Cache (LLC)                          |        | 36 MB                             | 33 MB                             | 30 MB                             | 24 MB                             | 20 MB                             |  |

| Max Turbo Frequency <sup>10</sup>                 | P-core | Up to<br>5.8 GHz                  | Up to<br>5.5 GHZ                  | Up to<br>5.2 GHz                  | Up to<br>4.9 GHz                  | Up to<br>4.8 GHz                  |  |

| E-core                                            |        | Up to<br>4.1 GHz                  | Up to<br>3.9 GHz                  | Up to<br>3.7 GHz                  | Up to<br>3.5 GHz                  | Up to<br>3.5 GHz                  |  |

| Overclocking <sup>3</sup>                         | CPU    | ✓                                 | <b>*</b>                          | <b>*</b>                          | *                                 | <b>*</b>                          |  |

| GFX                                               |        | ✓                                 | ✓                                 | <b>✓</b>                          | <b>✓</b>                          | <b>✓</b>                          |  |

|                                                   | Memory | <b>✓</b>                          | ✓                                 | <b>✓</b>                          | <b>✓</b>                          | <b>*</b>                          |  |

| Graphics Max Frequency                            |        | Up to<br>1.65 GHz                 | Up to<br>1.6 GHz                  | Up to<br>1.6 GHz                  | Up to<br>1.55 GHz                 | Up to<br>1.5 GHz                  |  |

| Processor Graphics                                |        | Intel® UHD Graphics               |                                   |                                   |                                   |                                   |  |

| Total PCIe Lanes                                  |        | 1x15 Gen5 + 1x4 Gen4 (CPU)        |                                   |                                   |                                   |                                   |  |

| Max Memory Speed <sup>9</sup>                     |        | DDR5-5600, DDR4-3200              |                                   |                                   |                                   |                                   |  |

# 1.1. Evolution of the Intel's $\mu Ps$ .

Intel® Core Desktop Processors Comparison

|                                                       | Intel Core i9<br>Processors  | Intel Core i7<br>Processors | Intel Core i5<br>Processors |                        |

|-------------------------------------------------------|------------------------------|-----------------------------|-----------------------------|------------------------|

| Max Turbo Frequency [GHz]                             | Up to 6.0                    | Up to 5.6                   | Up to 5.3                   | Up to 4.7              |

| Intel® Turbo Boost Max Technology 3.0 Frequency [GHz] | Up to 5.8                    | Up to 5.6                   | N/A                         | N/A                    |

| Performance-core Max Turbo Frequency [GHz]            | Up to 5.6                    | Up to 5.5                   | Up to 5.1                   | Up to 4.7              |

| Efficient-core Max Turbo Frequency [GHz]              | Up to 4.4                    | Up to 4.3                   | Up to 3.9                   | N/A                    |

| Processor Cores (P-cores + F-cores)                   | 24 (8P + 16F)                | 20 (8P + 12F)               | 14 (6P + 8E)                | 4 (4P + 0F)            |

| Intel® Hyper-Threading Technology                     | Yes                          |                             |                             |                        |

| Total Processor Threads                               | 32                           | 28                          | 20                          | 8                      |

| Intel® Thread Director                                | Yes                          |                             |                             | No                     |

| Intel® Smart Cache (L3) Size [MB]                     | 36 MB                        | 33 MB                       | 24 MB                       | 12 MB                  |

| Total L2 Cache Size [MB]                              | 32 MB                        | 28 MB                       | 20 MB                       | 5 MB                   |

| Max Memory Speed [MT/s]                               | Up to DDR5-5600<br>DDR4-3200 |                             |                             | DDR5 4800<br>DDR4 3200 |

The execution time are given as:

| 8080      | 2 μs   |

|-----------|--------|

| 8085      | 1.3 μs |

| 8086/8088 | 400 ns |

- The advantages of the 8086/8088:

- Hardware multiplication and division.

- Larger addressable memory space.

- Large number of internal registers which are accessible in 200 ns.

## 1.2. 8086/8088 Architecture

- The steps of fetching and executing the instruction:

- 1. An instruction is fetched from memory, then it is decoded within the  $\mu P$ .

- 2. Operands are read from/written to either the data memory segment or internal registers.

- 3. The  $\mu P$  is now ready to execute the next instruction.

## 1.2. 8086/8088 Architecture

The normal operation of an 8085 is

CPU

Fetch

Read

Execute

Fetch

Write

Execute

Busy Busy Busy Busy

## 1.2. 8086/8088 Architecture

The normal operation of an 8086/8088 depends on pipelining

EUExecuteExecuteBIUFetchReadFetchWriteFetchBusBusyBusyBusyBusyBusy

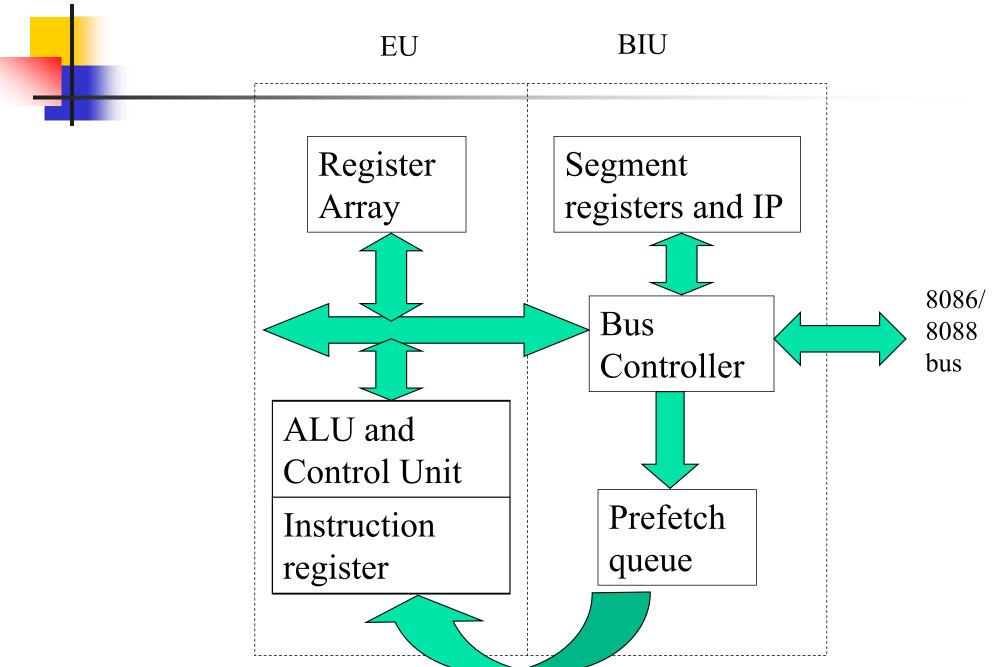

## 2.1. Basic Internal Architecture

# 1.2.1.1. Bus Interface Unit (BIU)

- The main purposes of the BIU are:

- To keep the prefetch queue filled with instructions.

- 2. To generate and accept the system control signals.

- 3. To provide the system with the memory address or I/O port number.

- 4. To act as window between the EU and memory for data.

# 1.2.1.1. Bus Interface Unit (BIU)

- The prefetch queue is FIFO memory.

- The 8086 queue is 2 byte-wide queue and 3 locations deep.

- The 8088 queue is a byte-wide queue and 4 bytes deep.

## 1.2.1.2. Execution Unit (EU)

- The EU carries out instructions that are fetched from the prefetch queue.

- The ALU performs arithmetic and logic operations on memory or register data.

- The register array holds information temporarily

- The instruction register

- Receives the instruction from the prefetch queue.

- Decodes the instruction to be executed.

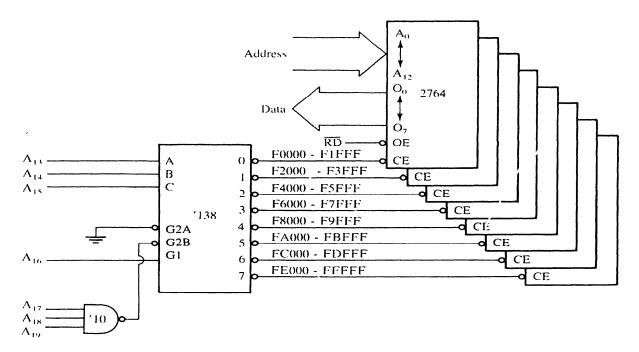

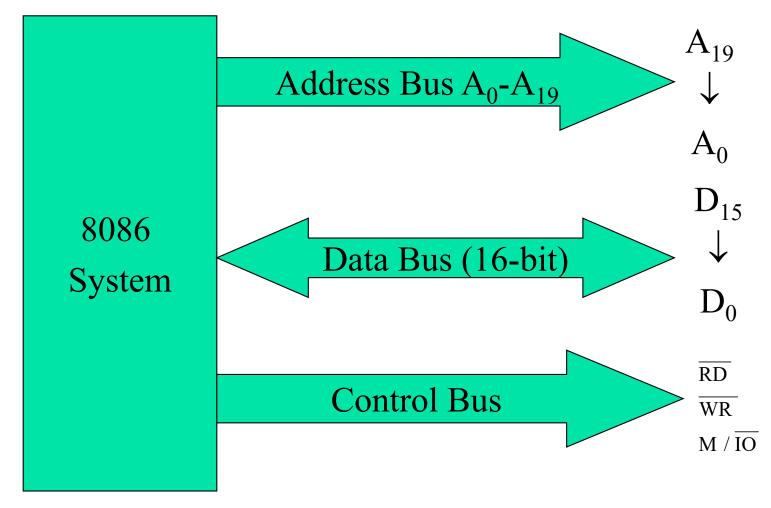

# 1.2.2. System Architecture

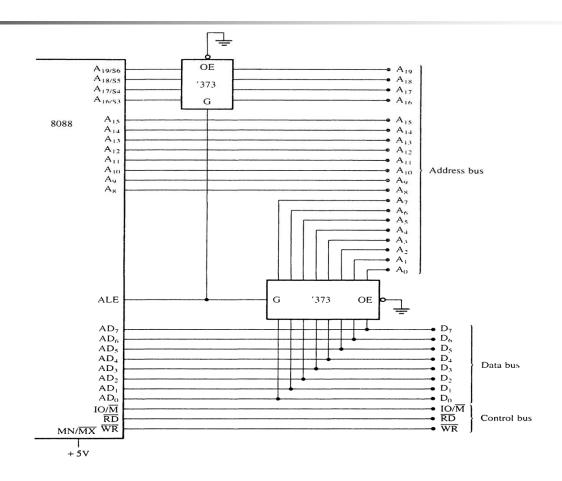

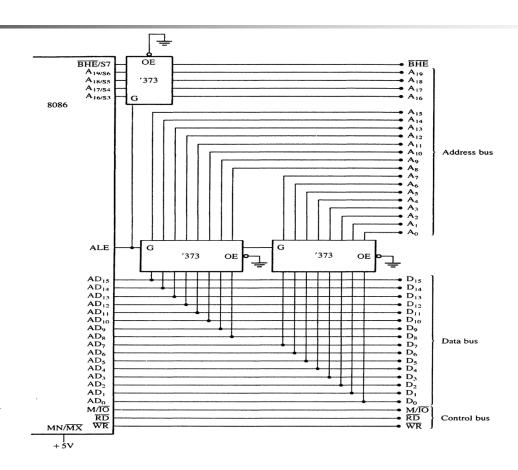

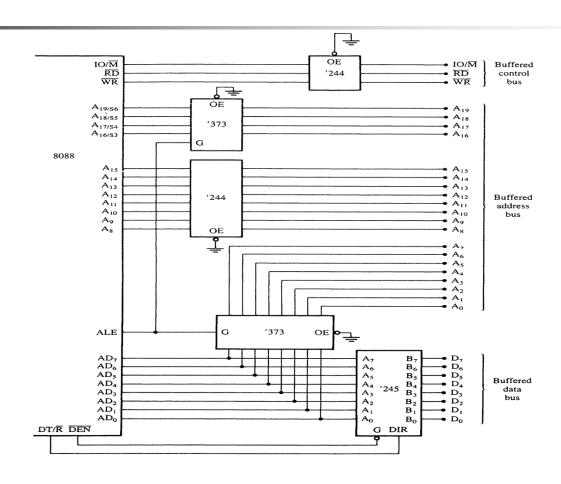

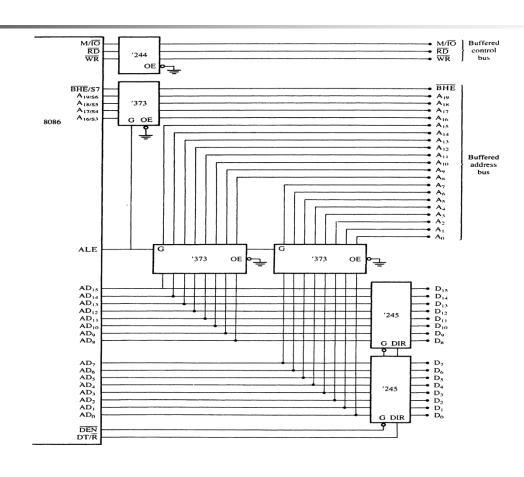

The 8086 system

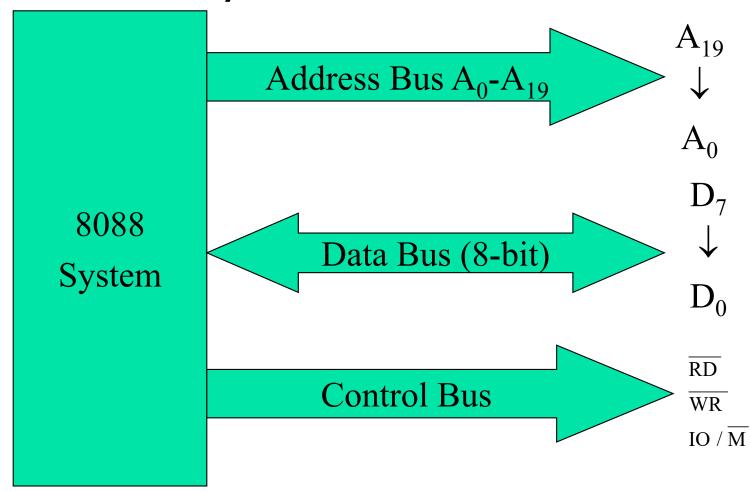

# 1.2.2. System Architecture

The 8088 system

# Lecture\_2

# 1.3. 8086/8088 Memory

- 8086/8088 has 1M (1,048,576) Byte.

- The memory can be studied from two pointsof-view:

- The programmer  $\Rightarrow$  Logical Memory.

- The hardware designer  $\Rightarrow$  Physical Memory.

# 1.3.1. Logical Memory

The logical memory is the same for both 8086 and 8088 μPs.

> **FFFFFH** 1M Bytes

# 1.3.1. Logical Memory

Some address locations have dedicated functions or reserved.

FFFFFH

**FFFFCH**

FFFF0H

Reserved

Dedicated

Open for

0007FH

00014H

H00000

general Use

Reserved

Dedicated

For future use

For functions such as storage of the hardware reset jump instructions.

For Interrupt

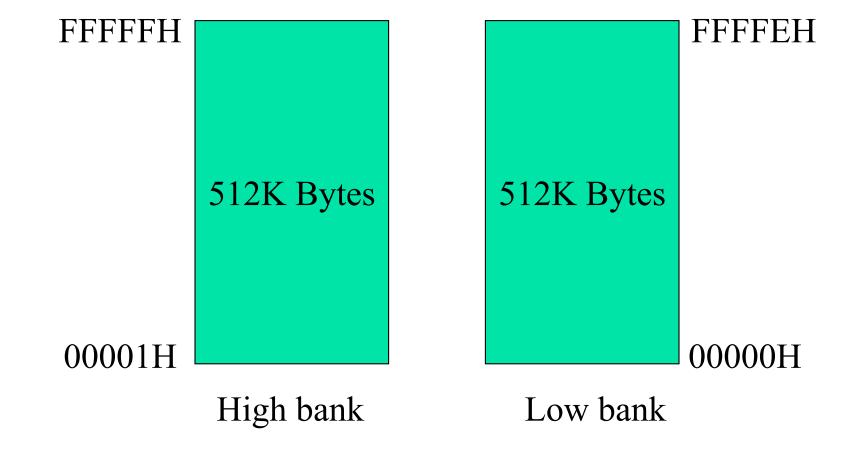

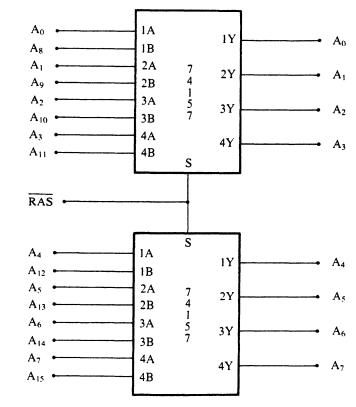

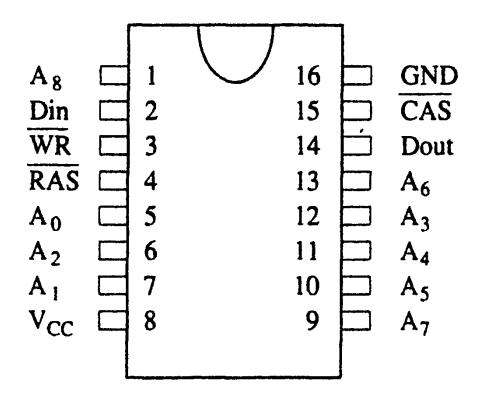

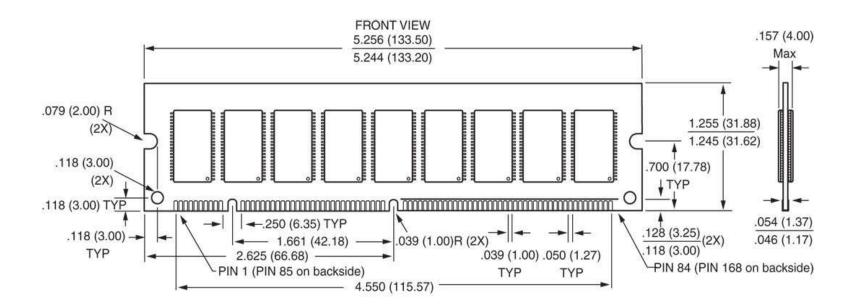

# 1.3.2. Physical Memory

• The physical memory of the 8088  $\mu P$  is identical to its logical memory.

**FFFFFH** 1M Bytes 00000H

# 1.3.2. Physical Memory

The physical memory of the 8086 μP

# 1.3.2. Physical Memory

- The advantages of this organization is:

- The 8086 can address any byte or word of data.

- To transfer 16 bits from/to memory:

- 8086 requires 1 operation.

- 8088 requires 2 operations.

- The 8086 software executes more efficiently.

# 1.4. Registers

- The registers can be divided into:

- Data or general purpose registers.

- Pointer and index registers.

- Segment registers.

- Flag register.

- There are 4 general-purpose data registers.

- Used for temporary storage of frequently used intermediate results.

- The advantage of storing the data in the internal registers instead of the memory is that they can be accessed much faster.

These registers can be used to store byte or word.

| AX |

|----|

| BX |

| CX |

| DX |

| AH | AL |

|----|----|

| BH | BL |

| СН | CL |

| DH | DL |

16 bits

8 bits

8 bits

- The primary functions of these registers include:

- AX (Accumulator)

- Used with the arithmetic and logic operation.

- 2. Used with the I/O devices

- BX (Base)

- Hold the base address of data located in the memory.

- 2. Hold the base address of a table of data referenced by the translate instruction (XLAT).

- The primary functions of these registers include:

- CX (Count)

- Used as a counter for certain instructions such as shift rotate and loop.

- 2. Used as a counter for the string operations.

- DX (Data)

- Used with the arithmetic instruction such as 16bit multiplication and division.

- 2. Hold the I/O port number for a variable I/O instruction.

There are five pointer and index registers.

SP (Stack Pointer)

BP (Base Pointer)

IP (Instruction Pointer)

DI (Destination Index)

SI (Source Index)

# 1.4.2. Pointers & Index Registers

- The functions of these registers are:

- SP (Stack pointer)

- Used to address data in a LIFO (last-in, first-out) stack memory.

- Used with the PUSH and POP instructions and the subroutines.

- BP (Base pointer)

- 1. Used to address an array of data in the stack memory.

# 1.4.2. Pointers & Index Registers

- The functions of these registers are:

- SI (Source index)

- Used to address the data.

- 2. Used with the string instructions.

- DI (Destination index)

- Used to address the data.

- 2. Used with the string instructions.

# 1.4.2. Pointers & Index Registers

- The functions of these registers are:

- IP (Instruction Pointer)

- Used to address the next instruction executed.

- Every time an instruction is fetched from memory, the 8086/8088 updates the value in IP such that it points to the first byte of the next instructions.

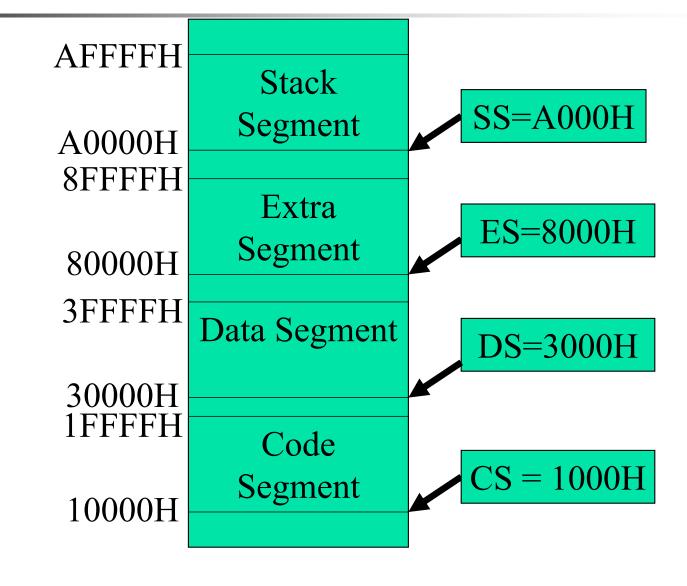

- The memory is 1M-byte.

- It can be partitioned into 64K (65536) byte segments.

- Not all this memory segments can be active at one time.

- Four segments only can be active at one time.

- 1. Code segment  $\Rightarrow$  store the program or code.

- 2. Data segment  $\Rightarrow$  store the data.

- 3. Stack segment  $\Rightarrow$  store data as LIFO stack.

- 4. Extra segment  $\Rightarrow$  used for string instructions.

- Each segment is addressed independently by a special register called a segment register.

- There are 4 segments registers

- CS

- DS

- SS

- ES

- Each segment register identifies the segment's starting point or its lowestaddressed byte.

- Each register is 16-bit wide.

- Each segment should start at address ended by 0000B.

- The leftmost 16 bit are stored at the segment registers.

- Examples:

| Segment Register | Memory Address Range |

|------------------|----------------------|

| 0100H            | 01000-10FFFH         |

| 1200H            | 12000H-21FFFH        |

| 2000H            | 20000H-2FFFFH        |

- In the segment, data are addressed by the registers.

- $CS \Rightarrow IP$

- DS  $\Rightarrow$  BX, SI, DI.

- SS  $\Rightarrow$  BP, SP

- ES  $\Rightarrow$  DI

- The address of any memory location is 20 bits.

- The size of the registers is 16 bits.

- Question:

How can the registers point to any memory location?

# Lecture\_3

- There are logical and physical address.

- A logical address is described by

- The address stored at the segment register

- An offset stored at the index registers, pointer registers, base registers or instruction pointer.

- Both the segment and the offset are 16 bits long.

- It can be written as: Segment:Offset

- Example: CS:0100H

# 1.4.3.1. Generating a memory address

The physical address is computed as follows:

PA = Segment × 10H + Offset.

#### Example :

The segment register = 1000H and the Offset = 1234H

The physical address =  $1000 \times 10 + 1234 = 11234H$ .

# 1.4.3.1. Generating a memory address

#### Example1:

CS = 1000H, DS = 3000H, SS = A000H, ES = 8000H BX = 0200H.

• The physical address pointed to by the BX is  $DS \times 10 + BX = 30200H$ .

# 1.4.4. Flag Register

- The flag or status register is 16-bit register. within the 8086/8088.

- The state of these flags indicates the conditions that are produced as the result of executing an arithmetic or logic instruction.

- There are nine flags divided into two groups:

- Status flags: CF, PF, AF, ZF, SF and OF.

- Control flags: TF, IF and DF.

### 1.4.4. Flag Register

The flags are arranged as shown:

|  |  | $\mathbf{O}$ | D | Ţ | Т | S      | 7. | A | Р | C |

|--|--|--------------|---|---|---|--------|----|---|---|---|

|  |  |              |   | _ | _ | $\sim$ |    |   | - |   |

- The function of these flags are:

- 1. Carry flag (CF)

CF = 1 if there is a carry or borrow.

CF = 0 otherwise

Parity flag (PF)

PF = 1 if the result contains an even number of 1's.

PF = 0 if the result has an odd number of 1's.

# 4

## 1.4.4. Flag Register

- The function of these flags are:

- Auxiliary carry flag (AF)

AF = 1 if there is a carry-out or a borrow-in between the low and high nibble.

AF = 0 if there is no carry-out or borrow-in.

Zero flag (ZF)

ZF = 1 if the result is zero.

ZF = 0 if the result is not zero.

5. Sign flag (SF)

SF = 1 if the result is negative number.

SF = 0 if the result is positive number.

# 1.4.4. Flag Register

- The function of these flags are:

- 6. Trap flag (TF)

TF = 1 if the  $\mu$ P works in the single-step mode.

TF = 0 if the 8086/8088 works in normal mode.

Interrupt flag (IF)

IF = 1 if the  $\mu$ P enables the maskable interrupt.

IF = 0 if the  $\mu$ P disables the maskable interrupt.

# 1.4.4. Flag Register

- The function of these flags are:

- 8. Direction flag (DF)

DF = 1 if the string instruction automatically decrements the address.

DF = 0 if the string instruction automatically increments the address.

Overflow flag (OF)

OF = 1 if the signed result is out of range.

OF = 0 of the signed result is within the range.

#### 1.5. Data Formats

- The data can be presented as:

- ASCII

- BCD

- 8-bit signed and unsigned integers.

- 16-bit signed and unsigned integers.

- 32-bit signed and unsigned integers.

- Short and long real numbers (floating-point numbers).

#### 1.5.1. ASCII Data

- Used to represent alphanumeric characters.

- It is 7-bit code.

- In some systems, 8<sup>th</sup> bit holds the parity.

- In the printer system,

- The 8<sup>th</sup> bit holds 0 for alphanumeric.

- The 8<sup>th</sup> bit holds 1 for graphics characters.

### 1.5.1. ASCII Data

TABLE 2.6 ASCII and EBCDIC Codes in Hex.

| Character | ASCII | EBCDIC | Character | ASCII | EBCDIC | Character | ASCII | EBCDIC | Character | ASCII         | EBCDIC |

|-----------|-------|--------|-----------|-------|--------|-----------|-------|--------|-----------|---------------|--------|

| @         | 40    |        |           | 60    |        | blank     | 20    | 40     | NUL       | 00            |        |

| A         | 41    | C1     | a         | 61    | 81     | 1         | 21    | 5A     | SOH       | 01            |        |

| В         | 42    | C2     | ь         | 62    | 82     | "         | 22    | 7F     | STX       | 02            |        |

| C         | 43    | C3     | c         | 63    | 83     | #         | 23    | 7B     | ETX       | 03            |        |

| D         | 44    | C4     | d         | 64    | 84     | \$        | 24    | 5B     | EOT       | 04            | 37     |

| E         | 45    | C5     | e         | 65    | 85     | %         | 25    | 6C     | ENQ       | 05            |        |

| F         | 46    | C6     | f         | 66    | 86     | &         | 26    | 50     | ACK       | 06            |        |

| G         | 47    | C7     | g         | 67    | 87     | •         | 27    | 7D     | BEL       | 07            |        |

| H         | 48    | C8     | h         | 68    | 88     | (         | 28    | 4D     | BS        | 08            | 16     |

| I         | 49    | C9     | i         | 69    | 89     | )         | 29    | 5D     | HT        | 09            | 05     |

| J         | 4A    | D1     | j         | 6A    | 91     | *         | 2A    | 5C     | LF .      | 0A            | 25     |

| K         | 4B    | D2     | k         | 6B    | 92     | +         | 2B    | 4E     | VT        | 0B            |        |

| L         | 4C    | D3     | 1         | 6C    | 93     | ,         | 2C    | 6B     | FF        | 0C            |        |

| M         | 4D    | D4     | m         | 6D    | 94     | -         | 2D    | 60     | CR        | 0D            | 15     |

| N         | 4E    | D5     | n         | 6E    | 95     |           | 2E    | 4B     | SO        | 0E            |        |

| O         | 4F    | D6     | 0         | 6F    | 96     | 1         | 2F    | 61     | SI        | $\mathbf{0F}$ |        |

| P         | 50    | D7     | P         | 70    | 97     | 0         | 30    | F0     | DLE       | 10            |        |

| Q         | 51    | D8     | q         | 71    | 98     | 1         | 31    | F1     | DC1       | 11            |        |

| R         | 52    | D9     | r         | 72    | 99     | 2         | 32    | F2     | DC2       | 12            |        |

| S         | 53    | E2     | s         | 73    | A2     | 3         | 33    | F3     | DC3       | 13            |        |

| T         | 54    | E3     | t         | 74    | A3     | 4         | 34    | F4     | DC4       | 14            |        |

| U         | 55    | E4     | u         | 75    | A4     | 5         | 35    | F5     | NAK       | 15            |        |

| V         | 56    | E5     | v         | 76    | A5     | 6         | 36    | F6     | SYN       | 16            |        |

| W         | 57    | E6     | w         | 77    | A6     | 7         | 37    | F7     | ETB       | 17            |        |

| X         | 58    | E7     | x         | 78    | A7     | 8         | 38    | F8     | CAN       | 18            |        |

| Y         | 59    | E8     | У         | 79    | A8     | 9         | 39    | F9     | EM        | 19            |        |

| Z         | 5A    | E9     | z         | 7A    | A9     | 1         | 3A    |        | SUB       | 1A            |        |

| ]         | 5B    |        | {         | 7B    |        | ;         | 3B    | 5E     | ESC       | 1B            |        |

| 1         | 5C    |        |           | 7C    | 4F     | <         | 3C    | 4C     | FS        | 1C            |        |

| 3         | 5D    |        | }         | 7D    |        | =         | 3D    | 7E     | GS        | 1D            |        |

| ^         | 5E    |        | ~         | 7E    |        | >         | 3E    | 6E     | RS        | 1E            |        |

| -         | 5F    | 6D     | DEL       | 7F    | 07     | ?         | 3F    | 6F     | US        | 1F            |        |

#### 1.5.2. BCD

- Binary Coded Decimal (BCD) is 4-bit binary codes from 0000 (0) to 1001 (9).

- It can be stored as:

- Packed BCD ⇒ 2 BCD digits / memory byte.

- Unpacked BCD  $\Rightarrow$  1 BCD digit / memory byte.

### 1.5.3. Byte

- Byte data are stored as:

- UnSigned

$0 \rightarrow 255$

#### Signed

**-128** → **127**

### 1.5.3. Byte

- The negative numbers are presented in its 2's complement.

- Example:

- If the value is 81H

As unsigned byte,  $81H = 129_{10}$ .

As signed byte,  $81H = (-128+1)_{10} = -127_{10}$ .

#### 1.5.4. Word

- Word data is formed as two bytes

- They are stored as:

- UnSigned

| $2^{15}$ | $2^{14}$ | $2^{13}$ | $2^{12}$ | $2^{11}$ | $2^{10}$ | $2^{9}$ | $2^{8}$ | $2^7$ | $2^6$ | $2^{5}$ | $2^4$ | $2^3$ | $2^2$ | $2^{1}$ | $2^{0}$ |

|----------|----------|----------|----------|----------|----------|---------|---------|-------|-------|---------|-------|-------|-------|---------|---------|

|          |          |          |          |          |          |         |         |       |       |         |       |       |       |         |         |

#### Signed

| -2 <sup>15</sup> | $2^{14}$ | $2^{13}$ | $2^{12}$ | $2^{11}$ | $2^{10}$ | $2^{9}$ | $2^{8}$ | $2^{7}$ | $2^{6}$ | $2^5$ | $2^4$ | $2^3$ | $2^2$ | $2^1$ | $2^0$ |

|------------------|----------|----------|----------|----------|----------|---------|---------|---------|---------|-------|-------|-------|-------|-------|-------|

|                  |          |          |          |          |          |         |         |         |         |       |       |       |       |       |       |

#### 1.5.4. Word

- To store the word in the memory,

- It takes two bytes (two memory locations).

- The least significant byte of the word is stored at the lower-addressed byte.

- The most significant byte is stored at the higheraddressed byte.

- Example: Store 1234H at address 10000H

| 10001H | 12 |

|--------|----|

| 10000H | 34 |

#### 1.5.5. Double Word

Double word is formed as 4 bytes.

Example: Store 12345678H at address

10000H.

| 10003H            | 12 |

|-------------------|----|

| 10002H            | 34 |

| 10002II<br>10001H | 56 |

|                   |    |

| 10000H            | 78 |

|                   |    |

#### 1.5.5. Double Word

Example: Store DS:Offset = 1000H:2356H at the address 10000H

| 10003H | 10 |

|--------|----|

| 10002H | 00 |

| 10001H | 23 |

| 10000H | 56 |

|        |    |

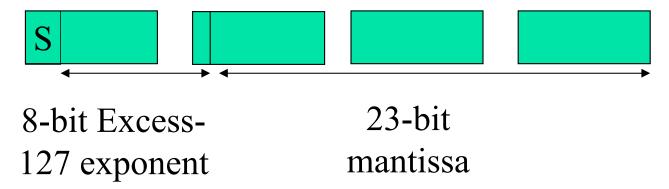

#### 1.5.6. Real Numbers

- A real or floating-point number is composed of:

- A mantissa

- An exponent.

- Example: Decimal 12 = 1100It can be written as  $1.1 \times 2^3$ The mantissa is 1 and the exponent is 3.

#### 1.5.6. Real Numbers

- It can be stored as:

- 4-byte short form.

8-byte long form.

#### 1.5.6. Real Numbers

#### Examples:

| Decimal | Binary  | Normalized          | Sign | Biased   | Mantissa                  |

|---------|---------|---------------------|------|----------|---------------------------|

|         |         |                     |      | Exponent |                           |

| +12     | 1100    | $1.1 \times 2^3$    | 0    | 10000010 | 1000000 00000000 00000000 |

| -12     | 1100    | $-1.1 \times 2^3$   | 1    | 10000010 | 1000000 00000000 00000000 |

| +100    | 1100100 | $1.1001 \times 2^6$ | 0    | 10000101 | 1001000 00000000 00000000 |

| -1.75   | 1.11    | $-1.11 \times 2^0$  | 1    | 01111111 | 1100000 00000000 00000000 |

| 0.25    | .01     | 1.0×2 <sup>-2</sup> | 0    | 01111101 | 0000000 00000000 00000000 |

| 0.0     | 0       | 0                   | 0    | 00000000 | 0000000 00000000 00000000 |

# Lecture\_4

# Chapter 2: Addressing Modes

- In this chapter, we will discuss:

- The addressing modes.

- The stack.

- There are two types of the addressing modes:

- Data addressing modes.

- Program memory addressing modes.

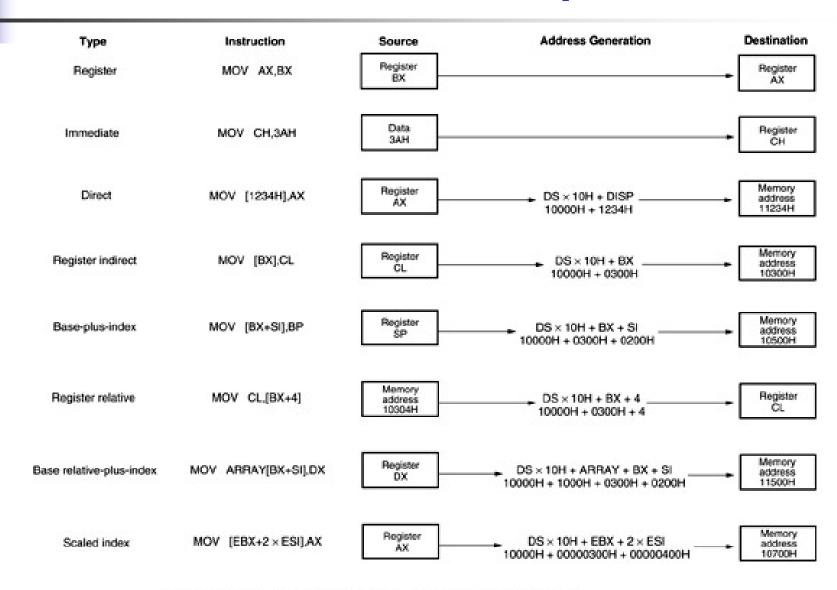

## 2.1. Data Addressing Modes

- MOV instruction is one of the simplest and most flexible instruction.

- It is written as:

MOV Destination, Source

- Move (copy) the data from the source to the destination.

- The addressing modes discuss how to describe the source and the destination.

## 1.2. Data Addressing Modes

- Data addressing modes are:

- a) Register Addressing.

- b) Immediate Addressing.

- c) Direct Addressing.

- d) Register Indirect Addressing.

- e) Base-Plus-Index Addressing.

- f) Register-Relative Addressing.

- g) Base-Relative-Plus-Index Addressing.

- i) Port Addressing.

- It is used to transfer a byte or word from the source register to the destination register.

- The 8-bit registers are AH,AL,BH,BL,CH,CL,DH,DL.

- The 16-bit registers are AX,BX,CX,DX,SP,BP,SI,DI,CS,DS,SS,ES.

- The rules of using this addressing mode:

- a) The source and destination registers have the same size.

- b) It is not allowed to MOV from one segment to another.

# 2.3. Register Addressing

## Examples on the register addressing

| Assembly Language | Operation           |

|-------------------|---------------------|

| MOV AL,BL         | $BL \rightarrow AL$ |

| MOV CH,CL         | $CL \rightarrow CH$ |

| MOV AX,CX         | $CX \rightarrow AX$ |

| MOV SP,BP         | $BP \rightarrow SP$ |

| MOV DS,AX         | $AX \rightarrow DS$ |

| MOV SI,DI         | $DI \rightarrow SI$ |

| MOV DI,SI         | $SI \rightarrow DI$ |

| MOV BX,ES         | $ES \rightarrow BX$ |

| MOV CS,DS         | Not allowed         |

| MOV BL,BX         | Not allowed         |

| MOV AX,DL         | Not allowed         |

# 2.3. Register Addressing

Example on the register addressing MOV BX,CX

Ex: Before execution

| AX |      |

|----|------|

| BX | 76AF |

| CX | 1234 |

| DX |      |

#### After execution

| AX |      |

|----|------|

| BX | 1234 |

| CX | 1234 |

| DX |      |

## 2.4. Immediate Addressing

- It is used to transfer the immediate byte or word of data to the destination register.

- The data is stored immediately in the instruction.

#### Examples

| Assembly Language | Operation              |

|-------------------|------------------------|

| MOV BL,44         | $2CH \rightarrow BL$   |

| MOV AX,44H        | $0044H \rightarrow AX$ |

| MOV SI,0          | 0000H → SI             |

| MOV CH,100        | 64H → CH               |

| MOV SP,3000H      | 3000H →SP              |

## 2.4. Immediate Addressing

Example on the Immediate addressing: MOV AX, 3456H

#### Before execution

| AX | 6291 H |

|----|--------|

| BX |        |

| CX |        |

| DX |        |

#### After execution

| AX | 3456H |

|----|-------|

| BX |       |

| CX |       |

| DX |       |

## 2.5. Direct Addressing

- It is used to transfer a byte or word between the memory and a register.

- The memory address of the data is stored by its effective memory address or the offset.

- The physical address of the data is computed as: Segment Register × 10H + EA.

- The effective address can be written as:

- Direct (Label)

- Displacement

## 2.5.1. Direct Addressing

- The effective address is presented by the label.

- Example: MOV AX, BETA

- This stands for "move the contents of the memory location labeled as BETA into the register AX". The physical address of the data is DS×10H+BETA and DS×10H+BETA+1.

### Examples:

| Assembly Language | Operation                                              |

|-------------------|--------------------------------------------------------|

| MOV AL, NUMBER    | The contents of the memory location DS×10H+NUMBER is   |

|                   | copied, a byte, into AL.                               |

| MOV THERE,AX      | The content of the AX is copied to the memory location |

|                   | whose address is DS×10H+THERE and DS×10H+THERE+1       |

- Example: MOV AL, NUMBER1

- Where NUMBER1 = 1234H and DS = 1000H

- The PA = DS  $\times$ 10H + 1234 = 11234H

- Only with the AX, AL and AH registers

Ex: Before execution

| AH AL XX XX |

|-------------|

|-------------|

Memory

| Address | Content |

|---------|---------|

| 11234   | 12      |

| 11235   |         |

After execution

| AH | AL | XX | 12 |

|----|----|----|----|

# 2.5.2. Displacement Addressing

- The effective address is given in the instruction.

- Example: MOV CX, [1234H]

- This stands for "move the contents of the memory location whose effective address is 1234H into the register CX". The physical address of the data is DS×10H+1234H and DS×10H+1234+1.

#### Examples:

| Assembly Language | Operation                                                    |

|-------------------|--------------------------------------------------------------|

| MOV CL,[2000H]    | The contents of the memory location DS×10H+2000H is          |

|                   | copied a byte into CL.                                       |

| MOV THERE,BX      | The content of the BX is copied to the memory location whose |

|                   | address is DS×10H+THERE and DS×10H+THERE+1                   |

# 2.5.2. Displacement Addressing

- Example: MOV CX, [2000H]

where DS = 1000H

- Physical address = DS  $\times$ 10H + 2000H = 12000H

#### Before execution

| BH | BL | XX | XX |

|----|----|----|----|

| CH | CL | XX | XX |

#### Memory

| Address | Content |

|---------|---------|

| 12000   | ED      |

| 12001   | BD      |

| 12002   |         |

| 12003   |         |

#### After execution

| BH | BL | XX | XX |

|----|----|----|----|

| СН | CL | BD | ED |

# 2.6. Register Indirect

- It is used to transfer a byte or word between a register and the memory location addressed by a register.

- The data is addressed at the memory location pointed to by any of the following registers: BX, BP, SI and DI.

- An Example of this mode is given as: MOV AX,[SI]

- This stands for "move the content of memory location whose effective address is stored in SI to the register AX".

- The physical address is DS×10H+SI and DS  $\times$  10H+SI+1.

## 2.6. Register Indirect

The following table illustrates several MOV instructions using register indirect mode.

| Assembly Language | Operation                                                    |

|-------------------|--------------------------------------------------------------|

| MOV CX,[BX]       | The contents of the memory location DS×10H+BX and            |

|                   | DS×10H+BX+1 are copied as word into CX.                      |

| MOV [BP],DL       | The content of the DL is copied to the memory location whose |

|                   | address is SS×10H+BP.                                        |

| MOV [DI],BH       | The content of the BH is copied to the memory location whose |

|                   | address is ES×10H+DI.                                        |

# 2.6. Register Indirect

### Example: MOV AX, [SI]

#### Before execution

| AX | XXXX |

|----|------|

| SI | 1234 |

#### Memory: DS×10+SI=11234

| Address | Content |

|---------|---------|

| 11234   | 56      |

| 11235   | 87      |

|         |         |

#### After execution

| AX | 8756 |

|----|------|

| SI | 1234 |

### Example: MOV CX, [BP]

#### Before execution

| CX | XXXX |

|----|------|

| BP | 2000 |

#### Memory: SS×10+BP=22000

| Address | Content |

|---------|---------|

| 22000   | 56      |

| 22001   | 87      |

|         |         |

#### After execution

| CX | 8756 |

|----|------|

| BP | 2000 |

## 2.7. Base-Plus-Index Addressing

- It is used to transfer a byte or word between a register and the memory location addressed by a base register plus an index register.

- The base register holds the beginning address of a memory array.

- The index register holds the relative position of the data in the array.

## 2.7. Base-Plus-Index Addressing

Example: MOV [BX + SI], AL

"move the content of the register AL to the memory location whose effective address is the sum of the content of SI and the content of BX".

- The physical address = DS×10H+BX+SI

- Example:

| Assembly Language | Operation                                                    |

|-------------------|--------------------------------------------------------------|

| MOV CX,[BX+SI]    | The contents of the memory location DS×10H+SI+BX and         |

|                   | DS×10H+SI+BX+1 are copied as word into CX.                   |

| MOV [BP+DI],DL    | The content of the DL is copied to the memory location whose |

|                   | address is SS×10H+BP+DI.                                     |

# 2.8. Register Relative Addressing

- It is used to transfer a byte or word between a register and the memory location indicated by the sum of the content of a register and a direct or indirect displacement.

- The register can be BX, BP, SI or DI.

- Example: MOV [BX +BETA], AL This stands for "move the content of the register AL to the memory location whose effective address is the sum of BETA and the content of BX".

- The physical address is DS $\times$ 10H+BX+BETA.

# 2.8. Register Relative Addressing

### Examples:

| Assembly Language | Operation                                                    |

|-------------------|--------------------------------------------------------------|

| MOV CX,[BX]+BETA  | The contents of the memory location DS×10H+BX+BETA           |

|                   | and DS×10H+BX+BETA+1 are copied as word into CX.             |

| MOV [BP+NEWS],DL  | The content of the DL is copied to the memory location whose |

|                   | address is SS×10H+BP+NEWS.                                   |

| MOV CX,ARRAY[SI]  | The contents of the memory location DS×10H+SI+ARRAY          |

|                   | and DS×10H+SI+ARRAY+1 are copied as word into CX.            |

| MOV [DI]BETA,DL   | The content of the DL is copied to the memory location whose |

|                   | address is DS×10H+DI+BETA.                                   |

# 2.8. Register Relative Addressing

Examples: MOV [BX]+BETA, AL

#### Before execution

| AX | BEED |

|----|------|

| BX | 1000 |

Memory: DS×10+BX+BETA=11234

| Address | Content |

|---------|---------|

| 11234   | ED      |

| 11235   | 87      |

|         |         |

#### After execution

| AX | BEED |

|----|------|

| BX | 1000 |

Memory After = Memory Before "87ED"

# 2.9. Base-Relative-Plus-Index Addressing

- It is used to transfer a byte or word between a register and the memory location addressed by a base register plus an index register plus a displacement.

- An Example: MOV [BX][SI]BETA,AL This stands for "move the content of the register AL to the memory location whose effective address is the sum of BETA and the content of SI and the content of BX".

The physical address =  $DS \times 10H + BX + SI + BETA$ .

# 2.9. Base-Relative-Plus-Index Addressing

### Examples

| Assembly Language   | Operation                                                    |  |

|---------------------|--------------------------------------------------------------|--|

| MOV CX,[BX+SI+BETA] | The contents of the memory location DS×10H+SI+BX+BETA        |  |

|                     | and DS×10H+SI+BX+BETA+1 are copied as word into CX.          |  |

| MOV BETA[BP+DI],DL  | The content of the DL is copied to the memory location whose |  |

|                     | address is SS×10H+BP+DI+BETA.                                |  |

# 2.9. Base-Relative-Plus-Index Addressing

#### Example: MOV CX,[BP][DI]BETA

#### Before execution

| DI | 0200 |

|----|------|

| CX | XXXX |

| BP | 0400 |

Memory: SS×10+BP+DI+BETA= 20000+0400+0200+1234=21834

| Address | Content |

|---------|---------|

| 21834   | FC      |

| 21835   | AB      |

| 21836   |         |

| 21837   |         |

#### After execution

| DI | 0200 |

|----|------|

| CX | ABFC |

| BP | 0400 |

## Summary

Notes: EBX = 00000300H, ESI = 00000200H, ARRAY = 1000H, and DS = 1000H

# Lecture\_5

# Chapter 4. Data Movement Instructions

- In this chapter, we will discuss the data movement instructions.

- These instructions are provided to move data either between its internal registers or between an internal register and a memory location.

- All these instructions do not affect the flags.

## 4.1. MOV

- MOV is used to transfer a byte or a word of data from a source operand to a destination operand.

- The following table shows this instruction:

| Mnemonic | Meaning | Format  | Operation             | Flags<br>affected |

|----------|---------|---------|-----------------------|-------------------|

| MOV      | Move    | MOV D,S | $(S) \rightarrow (D)$ | None              |

## 4.1. MOV

These operands take different forms as shown in the following table:

| Destination      | Source           |  |

|------------------|------------------|--|

| Memory           | Accumulator      |  |

| Accumulator      | Memory           |  |

| Register         | Register         |  |

| Register         | Memory           |  |

| Memory           | Register         |  |

| Register         | Immediate        |  |

| Memory           | Immediate        |  |

| Segment Register | Register-16      |  |

| Segment Register | Memory-16        |  |

| Register-16      | Segment Register |  |

| Memory           | Segment Register |  |

## 4.1. MOV

- The rules of the MOV instruction:

- It cannot transfer data directly between two memory locations.

- It cannot transfer data between two segment registers.

- The source and the destination have the same size.

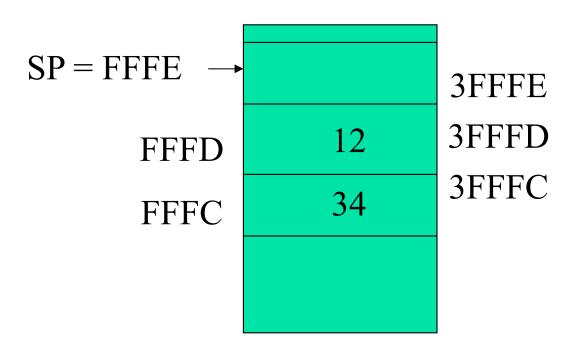

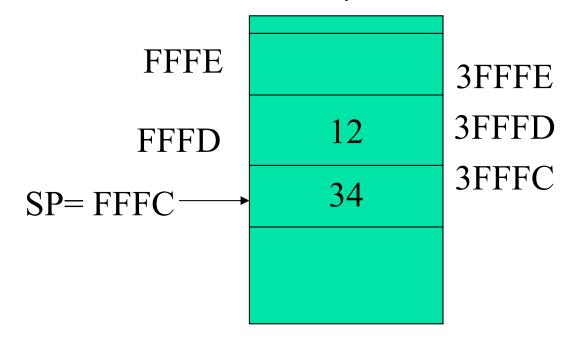

## 4.2. PUSH/POP

- Stack segment has 64K bytes.

- \* SS register is used to store the lowest address in the stack segment.

- **SP** is used to point to the top of the stack.

- \* There are four instructions to move the word data between the registers and the stack:

PUSH, POP, PUSHF and POPF.

## 4.2. PUSH/POP

### The following table shows these instructions

| Mnemonic | Meaning               | Format | Operation                   | Flags affected |

|----------|-----------------------|--------|-----------------------------|----------------|

| PUSH     | Push word onto stack  | PUSH S | $((SP)) \leftarrow (S)$     | None           |

| POP      | Pop word from stack   | POP D  | $(D) \leftarrow ((SP))$     | None           |

| PUSHF    | Push flags onto stack | PUSHF  | $((SP)) \leftarrow (flags)$ | None           |

| POPF     | Pop flags from stack  | POPF   | $(flags) \leftarrow ((SP))$ | None           |

- **★**The operand take the following forms:

- Register

- Memory

- Segment registers

- Flag Register

## 4.3. Load Effective-Address

- \* There are three load effective-address instructions used to load a register or a register and a segment register with an address.

- \* The following table shows these instructions:

| Mnemonic | Meaning                | Format          | Operation                     | Flags    |

|----------|------------------------|-----------------|-------------------------------|----------|

|          |                        |                 |                               | affected |

| LEA      | Load effective address | LEA Reg16,EA    | (EA)→(Reg16)                  | None     |

| LDS      | Load register          | LDS Reg16,Mem32 | $(Mem32) \rightarrow (Reg16)$ | None     |

|          | and DS                 |                 | $(Mem32+2)\rightarrow (DS)$   |          |

| LES      | Load register          | LES Reg16,Mem32 | $(Mem32) \rightarrow (Reg16)$ | None     |

|          | and ES                 |                 | $(Mem32+2)\rightarrow (ES)$   |          |

## 4.3.1. LEA

- It is used to load a register with the address of the data specified by the operand, not the data.

- By comparing an LEA with a MOV:

- LEA BX,[DI] ; loads the address specified by [DI] into the BX register BX=DI.

- MOV BX,[DI]; load the data stored at the memory location addressed by DI into BX.

- LEA BX,[DI] is equivalent to MOV BX,DI.

## 4.3.1. LEA

- Example 1: LEA CX, [DI]

Before Execution: CX = 1000H, DI = 2000H

- After Execution: CX = 2000H, DI = 2000H

- Example 2: LEA CX, [BX+DI]

- If BX = 1000H and DI = 2000HAfter the execution CX = BX + DI = 3000H.

- If BX = 1000H and DI = FF00H

After the execution CX = BX + DI = 0F00H.

## 4.3.2. LDS and LES

| Mnemonic | Meaning              | Format          | Operation                                  | Flags    |

|----------|----------------------|-----------------|--------------------------------------------|----------|

|          |                      |                 |                                            | affected |

| LDS      | <b>Load</b> register | LDS Reg16,Mem32 | $(Mem32) \rightarrow (Reg16)$              | None     |

|          | and DS               |                 | $(Mem32+2) \rightarrow (DS)$               |          |

| LES      | Load register        | LES Reg16,Mem32 | $(Mem32) \rightarrow (Reg16)$              | None     |

|          | and ES               |                 | $(\text{Mem32+2}) \rightarrow (\text{ES})$ |          |

- They load a 16-bit register with an offset address and either the DS or ES segment register with a new segment address.

- They use any of the valid memory addressing modes.

# 4

#### 4.3.2. LDS and LES

#### Example 1:

What is the result of executing: LDS SI,[200]?

Before Execution: DS = 1200H, SI = 0001H

| Address | Contents |

|---------|----------|

| 12203   | 13       |

| 12202   | 00       |

| 12201   | 00       |

| 12200   | 20       |

$$PA = DS \times 10 + 200 = 12200H$$

After Execution: SI = 0020H, DS = 1300H

### 4.3.2. LDS and LES

#### Example 2:

What is the result of executing: LES BX,[DI]?

Before Execution:

$$BX = 0000H$$

,  $DS = 1000H$ ,  $DI = 1000H$

$$PA = DS \times 10 + DI = 11000H$$

| Address | Contents  |

|---------|-----------|

| 11003   | 89        |

| 11002   | 30        |

| 11001   | <b>6F</b> |

| 11000   | 2A        |

After Execution: BX = 6F2AH, ES = 8930H

- There are three string data transfer instructions: LODS, STOS and MOVS.

- Each instruction allows data to be transferred as a block or group or as a single byte or word.

- These instructions use:

- SI to point to the source data.

- DI to point to the destination data.

- D flag to select the auto-increment (D=0) or auto-decrement (D = 1) mode of operation for SI and DI during the string operation.

#### The following table shows these instructions:

| Mnemonic | Meaning                | Format | Operation                                                                                                                    | Flags<br>affected |

|----------|------------------------|--------|------------------------------------------------------------------------------------------------------------------------------|-------------------|

| MOVS     | Move<br>String         | MOVS   | $((ES)0+(DI)) \leftarrow ((DS)0+(SI))$ $(SI) \leftarrow (SI) \pm 1 \text{ or } 2$ $(DI) \leftarrow (DI) \pm 1 \text{ or } 2$ | None              |

| MOVSB    | Move<br>String Byte    | MOVSB  | $((ES)0+(DI)) \leftarrow ((DS)0+(SI))$ $(SI) \leftarrow (SI) \pm 1$ $(DI) \leftarrow (DI) \pm 1$                             | None              |

| MOVSW    | Move<br>String<br>Word | MOVSW  | ((ES)0+(DI)) ← ((DS)0+(SI))<br>((ES)0+(DI)+1)← ((DS)0+(SI)+1)<br>(SI) ← (SI) ± 2<br>(DI) ← (DI) ± 2                          | None              |

| LODS     | <b>Load String</b>     | LODS   | $(AL \text{ or } AX) \leftarrow ((DS)0+(SI))$<br>$(SI) \leftarrow (SI) \pm 1 \text{ or } 2$                                  | None              |

| STOS     | Store String           | STOS   | $((ES)0+(DI)) \leftarrow (AL \text{ or } AX)$<br>$(DI) \leftarrow (DI) \pm 1 \text{ or } 2$                                  | None              |

Example: What is the result of executing: LODSW? Before execution: DS = 1000H, SI = 1000H, AX = XXXXH, DF = 0

| Address | Contents |

|---------|----------|

| 11002   | FA       |

| 11001   | A0       |

| 11000   | 32       |

After the execution: DS = 1000H, SI = 1002H, AX = A032H, DF = 0

- In most applications, the string operations must be repeated in order to process arrays of data.

- This is done by inserting a repeat prefix before the instruction that is to be repeated.

- The repeat prefix is shown:

| Prefix | Used With  | Meaning                                       |

|--------|------------|-----------------------------------------------|

| REP    | MOVS, STOS | Repeat while not end of string. $CX \neq 0$ . |

Example 1: What is the function of this program?

LES DI,LIST1 ;Loads DI,ES by the first address

in the destination list (LIST1).

LDS SI,LIST2 ;Loads SI,DS by the first address

in the source list (LIST2).

CLD ;DF = 0 so select auto-increment

MOV CX,100 ;Loads the counter CX = 100

REP MOVSB ;Transfers 100 bytes from LIST2

to LIST1.

This program moves 100 bytes from LIST2 to LIST1

Example2: What is the function of this program?

LES DI, BUFFER ; Loads DI, ES by the first address

in the destination list.

MOV CX,10 ;Loads the counter CX = 10

CLD ;DF = 0 so select auto-increment

MOV AL,0 ;Clears AL

REP STOSB ;Stores AL in the memory location

addressed by [DI]

This program clears 10 memory locations whose starting address is BUFFER

Example3: What is the function of this program?

LES DI, BUFFER ; Loads DI, ES by the first address

in the destination list.

MOV CX,5 ;Loads the counter CX = 5

CLD ;DF = 0 so select auto-increment

MOV AX,0 ;Clears AX

REP STOSW ;Stores AX in the memory location

addressed by [DI]

This program clears 10 memory locations whose starting address is BUFFER

- These instructions are:

- XCHG

- LAHF and SAHF

- IN and OUT

- XLAT

### 4.5.1. XCHG

- It exchanges the contents of any register with the contents of any register or memory location.

- The following table shows these instructions:

| Mnemonic | Meaning  | Format   | Operation | Flags affected |

|----------|----------|----------|-----------|----------------|

| XCHG     | Exchange | XCHG D,S | (D)↔(S)   | None           |

\*The allowed operands for these instructions are shown in the following table:

| <b>Destination</b> | Source           |

|--------------------|------------------|

| Accumulator        | Register-16 bits |

| Memory             | Register         |

| Register           | Register         |

## 4.5.1. XCHG

Example: If BX = 11AAH, DS = 1200H and the memory location addressed by SUM contains 1E87 where SUM = 1234H.

What is the result of executing the following instruction: XCHG SUM, BX.

$PA = DS \times 10H + SUM = 12000 + 1234 = 13234H$

After the execution: BX = 1E87H and the memory locations (34 & 35 ) = 11AAH

## 4.5.2. LAHF and SAHF

- LAHF and SAHF transfer the least significant flag byte to and from the AH register.

- The following table shows these instructions:

| Mnemonic | Meaning             | Format | Operation                 | Flags affected |

|----------|---------------------|--------|---------------------------|----------------|

| LAHF     | Load AH from flags  | LAHF   | $(AH) \leftarrow (Flags)$ | None           |

| SAHF     | Store AH into flags | SAHF   | $(Flags) \leftarrow (AH)$ | SF,ZF,AF,PF,CF |

### 4.5.2. LAHF and SAHF

Example: Trace the following program.

MOV AL,0 ;Clears AL

LAHF ;Loads AH by the flags.

XCHG AH,AL ;Exchanges the data between AH

and AL.

SAHF ;Stores AH into the flags.

This program clears the SF,ZF,AF,PF,CF.

#### 4.5.3. IN and OUT

- The IN and OUT instructions are used to transfer the data between the I/O device and the microprocessor.

- This transfer goes through the AL or AX

- They use the port addressing mode.

#### 4.5.4. XLAT

- The XLAT (translate) instruction has been provided to simplify implementation of the lookup table operation.

- The following table shows this instruction:

| Mnemonic | Meaning   | Format                   | Operation                           | Flags    |

|----------|-----------|--------------------------|-------------------------------------|----------|

|          |           |                          |                                     | affected |

| XLAT     | Translate | <b>XLAT Source-table</b> | $((AL)+(BX)+(DS)0)\rightarrow (AL)$ | None     |

- **★**The procedure of this instruction:

- •It adds the contents of AL to the contents of the BX register to form a memory address in the data segment.

- •It loads the data stored at this address into the AL.

## 4.5.4. XLAT

Example: BCD-to-7-segment LED display

The 7-segment LED display lookup table is stored at location TABLE = 1000H in the data segment where DS = 4000H.

Write a program to convert the contents of the accumulator into 7-segment code. Assuming that the 7-segment code is already stored at TABLE.

#### 4.5.4. XLAT

The program is:

MOV BX, TABLE

MOV AL,05H

**XLAT**

;Initialize BX by the offset address

;Load AL by 5H (5 BCD number)

;AL will be loaded by the 7-segment code equivalent to 5.

$$;PA = DS \times 10 + BX + AL.$$

PA contains 6D (01101101) hgfedcba

## Lecture\_6

# Chapter 5. Arithmetic and Logic Instructions

- In this chapter, we will discuss the arithmetic and logic instructions.

- The execution of these instructions affects the status of the flags.

- The affected flags are carry flag (CF), sign flag (SF), zero flag (ZF), parity flag (PF) and overflow flag (OF).

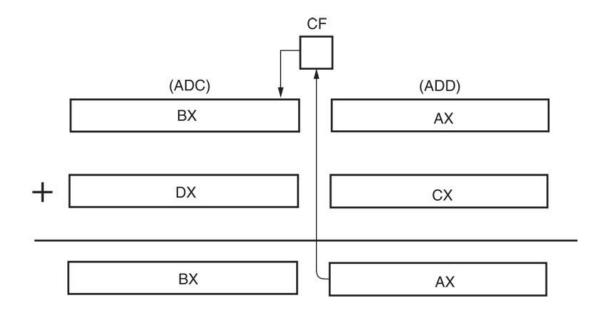

## 5.1. Addition

- Addition instructions include: ADD, ADC, INC.

- The following table shows these instructions:

| Mnemonic | Meaning        | Format  | Operation                    | Flags affected    |

|----------|----------------|---------|------------------------------|-------------------|

| ADD      | Addition       | ADD D,S | $(S)+(D)\rightarrow(D)$      | OF,SF,ZF,AF,PF,CF |

|          |                |         | $carry \rightarrow CF$       |                   |

| ADC      | Add with carry | ADC D,S | $(S)+(D)+(CF)\rightarrow(D)$ | OF,SF,ZF,AF,PF,CF |

|          |                |         | $carry \rightarrow CF$       |                   |

| INC      | Increment by 1 | INC D   | (D)+1→(D)                    | OF,SF,ZF,AF,PF,CF |

### 5.1. Addition

The allowed operands for ADD and ADC are:

| Destination | Source    |

|-------------|-----------|

| Register    | Register  |

| Register    | Memory    |

| Memory      | Register  |

| Register    | Immediate |

| Memory      | Immediate |

| Accumulator | Immediate |

The allowed operands for the INC

| Destination     |

|-----------------|

| Register-16 bit |

| Register-8 bit  |

| Memory          |

## 5.1. Addition

Example: What are the result of executing the following program:

| The program | Affected Register      | Affected flags                             |

|-------------|------------------------|--------------------------------------------|

| MOV AL, EDH | AL = EDH               | None                                       |

| ADD AL, 21H | AL = ED + 21 = 0EH     | ZF=0, CF=1, AF=0, SF=0, PF=0, OF=0.        |

| ADC AL,11H  | AL = 0E + 11 + 1 = 20H | <b>ZF=0, CF=0, AF=1, SF=0, PF=0, OF=0.</b> |

| INC AL      | AL = 20 + 1 = 21H      | <b>ZF=0, CF=0, AF=0, SF=0, PF=1, OF=0.</b> |

## 5.1.Subtraction

- Subtraction instructions include: SUB, SBB, DEC, NEG.

- The following table shows these instructions.

| Mnemonic | Meaning              | Format  | Operation                                                          | Flags affected |

|----------|----------------------|---------|--------------------------------------------------------------------|----------------|

| SUB      | Subtract             | SUB D,S | $(D)-(S)\rightarrow(D)$                                            | OF,SF,ZF,AF,   |

|          |                      |         | Borrow $\rightarrow$ CF                                            | PF,CF          |

| SBB      | Subtract with borrow | SBB D,S | $(D)-(S)-(CF)\rightarrow (D)$                                      | OF,SF,ZF,AF,   |

|          |                      |         | Borrow = CF                                                        | PF,CF          |

| DEC      | Decrement by 1       | DEC D   | (D)-1→(D)                                                          | OF,SF,ZF,AF,   |

|          |                      |         |                                                                    | PF,CF          |

| NEG      | Negate               | NEG D   | $0-(D) \to (D)$                                                    | OF,SF,ZF,AF,   |

|          |                      |         | $ \begin{array}{c} 0 \text{-}(D) \to (D) \\ 1 \to SF \end{array} $ | PF,CF          |

### 5.2. Subtraction

The allowed operands for SUB and SBB are:

| Destination | Source    |

|-------------|-----------|

| Register    | Register  |

| Register    | Memory    |

| Memory      | Register  |

| Register    | Immediate |

| Memory      | Immediate |

| Accumulator | Immediate |

The allowed operands for DEC and NEG are

| Destination     |

|-----------------|

| Register-16 bit |

| Register-8 bit  |

| Memory          |

## 5.2. Subtraction

Example: What are the result of executing the following program:

| The program          | Affected Register              | Affected flags                        |

|----------------------|--------------------------------|---------------------------------------|

| <b>MOV CX, 1527H</b> | CX = 1527H                     | None                                  |

| <b>MOV BX,1234H</b>  | $\mathbf{BX} = 1234\mathbf{H}$ | None                                  |

| SUB CX,44H           | CX=1527-0044=14E3              | <b>ZF=0,CF=0,AF=0,SF=0,PF=0,OF=0.</b> |

| SBB BX,CX            | BX=1234-14E3-0=FD51            | <b>ZF=0,CF=1,AF=0,SF=1,PF=0,OF=0.</b> |

| DEC BX               | BX = FD50H                     | <b>ZF=0,CF=0,AF=0,SF=1,PF=1,OF=0.</b> |

| NEG BX               | BX = 02B0H                     | <b>ZF=0,CF=1,AF=0,SF=0,PF=1,OF=0.</b> |

## 5.3. Multiplication

- \*\* Both 8- and 16-bit multiplication on either signed or unsigned numbers can be performed.

- \* This instruction results in shorter programs and faster execution.

- \* Multiplication always results in a double-width product.

- \* For example, if two 8-bit numbers are multiplied, then the product is always 16 bits.

- \* Likewise, if two 16-bit numbers are multiplied, then the product is always 32 bits.

## 5.3. Multiplication

- In 8-bit multiplication,

- The multiplicand is always in the AL register.

- The programmer can choose the multiplier.

- The 16-bit product is stored in AX.

- In 16-bit multiplication,

- The multiplicand is always in the AX register.

- The programmer can choose the multiplier.

- The 32-bit product is stored in DX and AX. DX will contain the most significant 16 bits of the products and AX will contain the least significant 16 bits.

- In the signed multiplication, the product is in true form if positive and in two's complement form if negative.

## 5.3. Multiplication

\* The following table shows these instructions:

| Mnemonic | Meaning    | Format | Operation                             | Flags affected    |

|----------|------------|--------|---------------------------------------|-------------------|

| MUL      | Multiply   | MUL S  | $(AL)\times(S8)\rightarrow(AX)$       | OF,SF,ZF,AF,PF,CF |

|          | (Unsigned) |        | $(AX)\times(S16)\rightarrow(DX),(AX)$ |                   |

| IMUL     | Multiply   | IMUL S | $(AL)\times(S8)\rightarrow(AX)$       | OF,SF,ZF,AF,PF,CF |

|          | (signed)   |        | $(AX)\times(S16)\rightarrow(DX),(AX)$ |                   |

\* The allowed operands are:

| Source          |

|-----------------|

| Register-8 bit  |

| Register-16 bit |

| Memory-8 bit    |

| Memory-16 bit   |

## •

## 5.3. Multiplication

Example 1: What are the results of this program:

```

MOV BL, 5 ;BL = 05H MOV CL, 10 ;CL = 0AH MOV AL, CL ;AL = 0A H MUL BL ;AX = AL \times BL = 0AH \times 05H = 32H

```

Example 2: IF AL = -1 = FFH and CL = -2 = FEH, what is the result of executing:

- Both 8- and 16-bit division on either signed (IDIV) or unsigned numbers (DIV) can be performed.

- Numbers are divided into its double-width dividend.

- For example, an 8-bit division always converts the 8-bit dividend into a 16-bit dividend.

- Likewise, in 16-bit division, the 16-bit dividend is always converted into 32-bit dividend.

- In 8-bit division,

- The dividend is located in AX register and the divisor is the operand selected for the instruction.

- The results are two 8-bit numbers: the quotient (AL) and the remainder in (AH).

- In 16-bit division,

- The dividend is located in DX and AX registers. DX will contain the most significant 16 bits of the dividend and AX will contain the least significant 16 bits.

- The results are two 16-bit numbers: the quotient in (AX) and the remainder in (DX).

- The signs of the remainder and the quotient are the same.

\* The following table shows these instructions:

| Mnemonic | Meaning    | Format | Operation                             | Flags affected    |

|----------|------------|--------|---------------------------------------|-------------------|

| DIV      | Division   | DIV S  | 1) $Q((AX)/(S8)) \rightarrow (AL)$    | OF,SF,ZF,AF,PF,CF |

|          | (Unsigned) |        | $R((AX)/(S8)) \rightarrow (AH)$       |                   |

|          |            |        | 2) $Q((DX,AX)/(S16))\rightarrow (AX)$ |                   |

|          |            |        | $R((DX,AX)/(S16))\rightarrow (DX)$    |                   |

| IDIV     | Division   | IDIVS  | 1) $Q((AX)/(S8)) \rightarrow (AL)$    | OF,SF,ZF,AF,PF,CF |

|          | (signed)   |        | $R((AX)/(S8)) \rightarrow (AH)$       |                   |

|          |            |        | 2) $Q((DX,AX)/(S16))\rightarrow (AX)$ |                   |

|          |            |        | $R((DX,AX)/(S16)) \rightarrow (DX)$   |                   |

\* The allowed operands are:

| Source          |

|-----------------|

| Register-8 bit  |

| Register-16 bit |

| Memory-8 bit    |

| Memory-16 bit   |

- There are two instructions (CBW and CWD) used before the division instructions.

- In 8-bit division, CBW (convert byte to word) converts the signed number in AL to a 16-bit signed number in AX.

- In 16-bit division, CWD (convert word to double word) converts the signed 16-bit number in AX to a 32-bit signed number in both DX and AX.

- The following table shows these instructions:

| Mnemonic | Meaning        | Format | Operation                                                    | Flags<br>affected |

|----------|----------------|--------|--------------------------------------------------------------|-------------------|

| CBW      | Convert B to W | CBW    | (MSB of AL)→(All bits of AH)                                 | None              |

| CWD      | Convert W to D | CWD    | $(MSB \text{ of } AX) \rightarrow (All \text{ bits of } DX)$ | None              |

# 4

## 5.4. Division

Example 1: What are the results of the following program:

MOV AL, A1H ; AL = A1H.

CBW ;AX = FFA1H

CWD; DX = FFFFH and AX = FFA1H.

Example 2: IF AX = 0012H and CL = 03H, what is the results of executing:

DIV CL

0012H/03H = 06H; The quotient is 6 and the remainder is 0

AX = 0006H

#### 5.4. Division

Example 3: What are the results of executing the following program:

```

MOV AX,-100 ;AX = -100 = -64H= FF9CH.

MOV CX,9 ;CX = 9 = 0009H.

CWD ; DX = FFFFH and AX = FF9CH

IDIV CX ; DX = -1 = FFFFH and

; AX = -11 = -000B H = FFF5H

```

#### 5.5. BCD and ASCII Arithmetic

- The 8086/8088 allows arithmetic manipulation of both binary coded decimal (BCD) and American Standard Code for Information Interchange (ASCII).

- BCD operations are used in applications that require little arithmetic, such as point of sales terminal (POS).

- ASCII operations are used in systems that employ ASCII-coded data to store numbers.

The following table shows these instructions:

| Mnemonic | Meaning                        | Format | Operation                                               | Flags affected    |

|----------|--------------------------------|--------|---------------------------------------------------------|-------------------|

| DAA      | Decimal adjust for addition    | DAA    |                                                         | OF,SF,ZF,AF,PF,CF |

| DAS      | Decimal adjust for subtraction | DAS    |                                                         | OF,SF,ZF,AF,PF,CF |

| AAM      | Adjust AL after multiplication | AAM    | $Q((AL)/10) \rightarrow AH$ $R((AL)/10) \rightarrow AL$ | OF,SF,ZF,AF,PF,CF |

| AAD      | Adjust AX before division      | AAD    | (AH)×10+AL→AL<br>00→AH                                  | OF,SF,ZF,AF,PF,CF |

- \* DAA, DAS and AAM are used after adding, subtracting or multiplying BCD numbers.

- \* The AAD instruction is used before a division to preadjust the numbers before using the DIV.

#### 5.5.1. BCD Arithmetic

Example: DAA (BX + DX)  $\rightarrow$  CX

Trace the following program

MOV DX, 1234H

MOV BX, 3099H

MOV AL, BL

ADD AL, DL

DAA

MOV CL, AL

MOV AL, BH

ADC AL, DH

DAA

MOV CH, AL

;DX = 1234H

;BX = 3099.

;AL=CDH

;AL = 33 and CF = 1

;AL = BH + DH + CF = 43H

; stays as is, it is a valid BCD

#### 5.5.1. BCD Arithmetic

Example: DAS (BX - DX) → CX Trace the following program MOV DX, 1234H ; DX = 1234HMOV BX, 3099H ;BX = 3099.MOV AL, BL SUB AL, DL DAS MOV CL, AL MOV AL, BH SBB AL, DH DAS MOV CH, AL

#### 5.5.1. BCD Arithmetic

Example: AAM (05 X 05)

Trace the following program

MOV AL, 5

MOV CL, 5

MUL CL

**AAM**

Example : AAD ( 72/9)

MOV AX, 0702H

MOV BL, 9

AAD

DIV BL

```

;AL = 05H

;CL = 05H

;AX now contains 0019H = 25

;AH = 02 and AL = 05

```

;makes AX = 48H;Q =  $08H \rightarrow AL R = 00H \rightarrow AH$

#### 5.5.2. ASCII Arithmetic

#### The following table shows these instructions:

| Mnemonic | Meaning                      | Format | Operation | Flags affected    |

|----------|------------------------------|--------|-----------|-------------------|

| AAA      | ASCII adjust for addition    | AAA    |           | OF,SF,ZF,AF,PF,CF |

| AAS      | ASCII adjust for subtraction | AAS    |           | OF,SF,ZF,AF,PF,CF |

- \* They are used with ASCII-coded numbers.

- \* These range from 30H through 39H and represent the number 0 through 9.

- \* They always use register AX as the source and destination.

TABLE 2.6 ASCII and EBCDIC Codes in Hex.

| Character    | ASCII | EBCDIC     | Character | ASCII      | EBCDIC | Character | ASCII | EBCDIC | Character | ASCII                  | EBCDIC |

|--------------|-------|------------|-----------|------------|--------|-----------|-------|--------|-----------|------------------------|--------|

| @            | 40    |            |           | 60         |        | blank     | 20    | 40     | NUL       | 00                     |        |

| A            | 41    | C1         | a         | 61         | 81     | 1         | 21    | 5A     | SOH       | 01                     |        |

| В            | 42    | C2         | ь         | 62         | 82     | **        | 22    | 7F     | STX       | 02                     |        |

| C            | 43    | C3         | c         | 63         | 83     | #         | 23    | 7B     | ETX       | 03                     |        |

| D            | 44    | C4         | d         | 64         | 84     | \$        | 24    | 5B     | EOT       | 04                     | 37     |

| E            | 45    | C5         | e         | 65         | 85     | %         | 25    | 6C     | ENQ       | 05                     |        |

| F            | 46    | C6         | f         | 66         | 86     | &         | 26    | 50     | ACK       | 06                     |        |

| G            | 47    | C7         | g         | 67         | 87     | 1 "       | 27    | 7D     | BEL       | 07                     |        |

| H            | 48    | C8         | h         | 68         | 88     | (         | 28    | 4D     | BS        | 08                     | 16     |

| I            | 49    | C9         | i         | 69         | 89     | )         | 29    | 5D     | HT        | 09                     | 05     |

| J            | 4A    | D1         | j         | 6A         | 91     | *         | 2A    | 5C     | LF ·      | OA                     | 25     |

| K            | 4B    | D2         | k         | 6B         | 92     | +         | 2B    | 4E     | VT        | $\mathbf{o}\mathbf{B}$ |        |

| L            | 4C    | D3         | 1         | 6C         | 93     | ,         | 2C    | 6B     | FF        | OC                     |        |

| M            | 4D    | D4         | m         | 6D         | 94     | -         | 2D    | 60     | CR        | OD                     | 15     |

| N            | 4E    | D5         | n         | 6E         | 95     |           | 2E    | 4B     | SO        | OE                     |        |

| 0            | 4F    | D6         | 0         | <b>6F</b>  | 96     | /         | 2F    | 61     | SI        | OF                     |        |

| P            | 50    | <b>D</b> 7 | p         | 70         | 97     | 0         | 30    | FO     | DLE       | 10                     |        |

| Q            | 51    | D8         | q         | 71         | 98     | 1         | 31    | F1     | DC1       | 11                     |        |

| R            | 52    | D9         | r         | 72         | 99     | 2         | 32    | F2     | DC2       | 12                     |        |

| S            | 53    | E2         | s         | 73         | A2     | 3         | 33    | F3     | DC3       | 13                     |        |

| T            | 54    | E3         | t         | 74         | A3     | 4         | 34    | F4     | DC4       | 14                     |        |

| U            | 55    | E4         | u         | 75         | A4     | 5         | 35    | F5     | NAK       | 15                     |        |

| V            | 56    | E5         | v         | 76         | A5     | 6         | 36    | F6     | SYN       | 16                     |        |

| w            | 57    | E6         | w         | 77         | A6     | 7         | 37    | F7     | ETB       | 17                     |        |

| $\mathbf{x}$ | 58    | <b>E</b> 7 | x         | 78         | A7     | 8         | 38    | F8     | CAN       | 18                     |        |

| Y            | 59    | E8         | У         | 79         | A8     | 9         | 39    | F9     | EM        | 19                     |        |

| Z            | 5A    | E9         | Z         | 7A         | A9     | 1         | 3A    |        | SUB       | 1A                     |        |

| ſ            | 5B    |            | {         | 7 <b>B</b> |        | ,         | 3B    | 5E     | ESC       | 1B                     |        |

| X            | 5C    |            | ] [       | 7C         | 4F     | <         | 3C    | 4C     | FS        | 1C                     |        |

| 3            | 5D    |            | { }       | 7 <b>D</b> |        | -         | 3D    | 7E     | GS        | 1D                     |        |

| ^            | 5E    |            | ~         | 7 <b>E</b> |        | >         | 3E    | 6E     | RS        | 1E                     |        |

|              | 5F    | 6D         | DEL       | 7F         | 07     | ?         | 3F    | 6F     | US        | 1F                     |        |

#### 5.5.2. ASCII Arithmetic

Example

MOV AX, 31H ; 31 is ASCII Code of 1

ADD AL, 39H ; 39 is ASCII code of 9

; results in 6AH

AAA ;clears AH if the sum is less than 10

; and adds 01H to AH if the sum is

; is greater than 10.

;AAA results in 01H in AH and 00H

; in AL...AX → 0100

ADD AX, 3030H; results in 3130 which is ASCII 10

# Lecture\_7

- The comparison instruction (CMP) is actually a subtraction that does not change anything except the flag bits.

- This instruction is almost always followed by a conditional jump instruction which tests the flag bits that are changed by CMP.

\* The following table shows this instruction